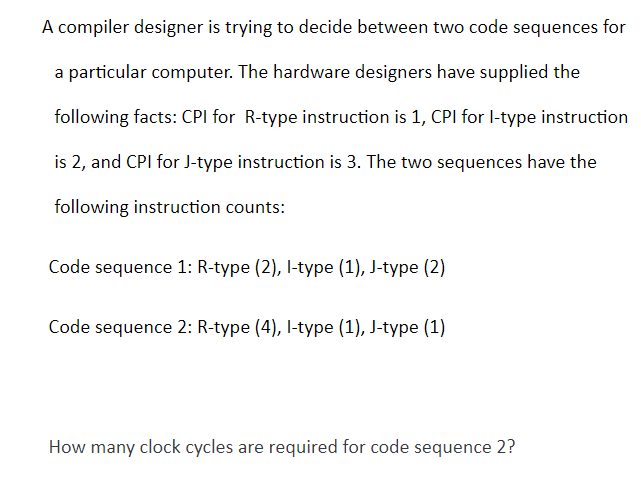

A compiler designer is trying to decide between two code sequences for a particular computer. The hardware designers have supplied the following facts: CPI for R-type instruction is 1, CPI for l-type instruction is 2, and CPI for J-type instruction is 3. The two sequences have the following instruction counts: Code sequence 1: R-type (2), l-type (1), J-type (2) Code sequence 2: R-type (4), l-type (1), J-type (1) How many clock cycles are required for code sequence 2?

Q: A CPU has an instruction pipeline with the following 4 segments. 1.F1(Fetch Instruction)…

A: EXPLANATION Below is the answer for the given question. Hope you understand it well. If you have any…

Q: (IMEM) - A read/write data memory (DMEM) This processor has 8 registers (R0-R7)

A: Design a simple microprocessor called Ege-ARM which is a simple 16-bit single-cycleprocessor that…

Q: Gain a greater understanding of the Intel 32-bit instruction set and understand how a compiler…

A: the solution is an given below ;

Q: Explain with a suitable Diagrams the three basic types of Computer Modules in your own words. Using…

A: Step 1 The Solution is given in the below step

Q: A compiler compiled a program into 25000 instructions. It is run on a processor with a clock…

A: See the solution below-

Q: MICROPROCESSOR EMULATOR CODES Solve all the given task through using assembly language code for…

A: mov ax,10 mov bx,20 add ax,bx sub bx,ax sub ax,bx Code to swap two numbers without using third…

Q: Design a simple microprocessor called Ege-ARM which is a simple 16-bit single-cycle processor that…

A: (A) * DATA PROCESSING:- data processing refers to transforming raw daa into meaningful output. DATA…

Q: Suppose the computer has an instruction format with space for an opcode and either three register…

A: Our computer has an instruction format with space for an opcode, three register values or one…

Q: Write MIPS assembly code implementing the following C/C++ statement: a[k*2-4] = a[k]*2 + 7;

A: Given C++ statement: a[k*2-4] = a[k]*2 + 7; To convert: Convert the given statement into MIPS…

Q: Write an assembly program for the processor family x86-32 that reads three signed interger numbers…

A: The below is the answer:

Q: Given the X86-64 assembly instructions below, suppose variable "a" and "b" are long int data…

A: Lets do this line by line : 1. movq %rbx , %edx This moves the contents of register rbx into edx.…

Q: Microprocessor lab tasks - Solve the problems in assembly language using emu8086 solution…

A: 1) ; You may customize this and other start-up templates; ; The location of this template is…

Q: The following is the high level language instruction: X= X+Y. Choose the correct instruction for…

A: High- level language instruction - X = X+Y First, Load a register with the content of X Then, add…

Q: Consider a program having following sequence of instructions, where the syntax consists of an opcode…

A:

Q: The following Mic1 microcode excerpt shows support for a possible 7 bit opcode, 8 bit integer…

A: Given is shown below:

Q: The purpose of this project is to gain a greater understanding of the Intel 32-bit instruction set…

A: It is defined as a effective standard-motive programming language. It can be used to expand software…

Q: In this classification, each instruction is executed uşing its own input data, independently of how…

A: While doing programming in any programming language, you need to use various variables to store…

Q: Assume that we compile a program with two different compilers for the same ISA, then run the two…

A:

Q: Write an assembly language instruction that has five WORD size variables in its data section as…

A: Write an assembly language program that adds num1 + num2 + num3 + num4 and places the result in…

Q: “Assembly Program is a machine dependent code”-Justify the statement. MOV CS, AX. Identify the…

A: MOV CS.AX is the wrong instruction. Here CS is a segment register(Code Segment). Segment register…

Q: Consider an assembly language that has a 2-address ISA set. | The instructions that are available in…

A: Given registers R1, R2, R3 and we cant change original values of operands and 4 value is cant take…

Q: the following program in MARIE assembly language. a) Complete the table detailing the RTN for next 2…

A: It is defined as a low-level programming language for a computer or other programmable device…

Q: Assembler Language VAR1 DS F VAR2 DS 5F Subtract VAR1 from VAR2. To do this, load these VARs…

A: We need to provide snippet of above line code with explanation.

Q: The steps performed by the Little Man Computer (LMC) are important because they reflect closely the…

A: An instruction model of the computer called Little Man Computer. It has simple von Neumann…

Q: Change the method of passing parameters so that the SI register acts as a pointer to the first…

A: Change the method of passing parameters so that the SI register acts as a pointer to the first…

Q: It is feasible to set up a compiler for assembly language and an assembler in such a way that a…

A: Given: Compilers and assemblers may be programmed to sequence assembly language instructions in…

Q: Insert a piece of assembler code into the C-program to calculate the sum of two variables. Tip: You…

A: A assembler is a program which takes basic computer program or instructions than it converts them…

Q: Consider the following program in MA dE assembly language. a) Complete the table detailing the RTN…

A: It is defined as a low-level programming language for a computer or other programmable device…

Q: Assembly for an Instruction 1 Suppose that a program contains this function int f(int a, int b) {…

A: Suppose the line .FILL #7 is having a label R. R be the name of the address where this instruction…

Q: Using the MARIE computer assembly language, write a program that computes the following expression:…

A: -> MARIE ('Machine Architecture that is Really Intuitive and Easy') is a machine architecture and…

Q: rite a program with comments to generate a delay of 0.25 s. if the microprocessor frequency is 2.5…

A: The hexadecimal counter is set by stacking a register with beginning number and decrementing it till…

Q: instruction formats

A: Solution :- An expression is given as X = (A*B)-(C/D) is specified in the above given question…

Q: A computer with a 32-bit word uses an instruction format that includes direct and indirect…

A: The answer given as below:·

Q: Push Рop Stack Pointer Тop Front Bottom Rear A LIFO Stack A FIFO queue

A: Example of stack & queue with number - Stack - stack works on Last In First out concept Queue -…

Q: Write down the machine code of the following assembly instructions for 8088/8086 processor in the…

A: Here i take all instruction and convert into machine code:…

Q: The condition known as orthogonality arises when the design of an instruction set includes a…

A: The CPU is required to perform the following tasks: The programme is executed using the code.

Q: The table below shows instruction-type breakdown for different programs. Using this data, you will…

A: The answer is

Q: Consider 4 WORD variables - var1, var2, var3 and var4. Translate the following code segment into…

A: The code given:- if (var1 > var2) AND (var2 < var3){ var1 = 5; } if ( var1 < var4){ var1 =…

Q: Orthogonality is the property of an instruction set design to have a "backup" instruction for every…

A: The CPU is required to perform the following tasks: The programme is executed using the code. The…

Q: Given the following assembly language program and its equivalent machine language code where some…

A: Answer: I have given answered in the handwritten format in brief explanation

Q: ing of the Intel 32-bit instruction set and understand how a compiler translates C code into…

A: Explanation: C is defined as a powerful general-purpose programming language. C language can be…

Q: hicroprocessor CPUS do not understand mnemonics as they are, they have to be converted to binary

A: Because microprocessor CPUs do not understand mnemonics as they are, they have to be converted to…

Q: The Problem Input File 55 67 gC programming language write a program that simulates a variant of the…

A: ANSWER:-

Q: what does the phrase "reduced" mean

A: check the step 2 for the means of phrase reduced

Q: Assembly Code with brief describe comments (EMU8086 emulator)

A: Answer 3).MODEL SMALL .DATA M1 DB 01H,01H,01H,01H,01H,01H,01H,01H,01H M2 DB…

Q: Gain a greater understanding of the Intel 32-bit instruction set and understand how a compiler…

A:

Q: The description of three-address instructions species the components of each type of instruction,…

A: In this question we need to write three-address code for the given expressions- Three-address code:-…

Q: Consider the instruction fields below: Op= 0, rs= 17 , rt= 3, rd= 4, shamt= 0, funct= 39 Provide the…

A: Answer:)

Trending now

This is a popular solution!

Step by step

Solved in 2 steps with 1 images

- A compiler designer is trying to decide between two code sequences for a particular machine. The hardware designers have supplied the following facts: Instruction class CPI of the instruction class A 1 B 3 C 4 For a particular high-level language, the compiler writer is considering two sequences that require the following instruction counts: Code sequence Instruction counts (in millions) A B C 1 2 1 2 2 4 3 1 a. What is the CPI for each code sequence? b. Which code sequence is faster? By how much?Compare compilers A and B for a program, where compiler A results in a dynamic instruction count of 6.9x10^9 and an execution time of 5 seconds, and compiler B results in a dynamic instruction count of 5.1x10^9 and an execution time of 4 seconds. a. Find the average CPI for each program, given a processor clock cycle time of 2 ns. b. If the compiled programs run on two different processors with the same execution times, what is the relative speed of the processor clocks?1. fast please in assembly language You are giving the before condition and an instruction. Give the after condition: Before: Eax: 00 00 00 0A Ebx: FF FF FF FB Edx: FF 03 FF 01 Instruction Executed: imul bx Group of answer choices 1.eax: 00 00 FF CE edx: FF 03 FF 01 2.eax: 00 00 FF CE edx: FF 03 FF FF 3.eax: 00 00 00 CE edx: 00 00 00 00 4.eax: FF FF FF CE edx: FF FF FF FF

- Microprocessor lab tasks - Solve the problems in assembly language using emu8086 solution format .MODEL SMALL .STACK 100H .DATA ; DEFINE YOUR VARIABLES HERE .CODE MAIN PROC MOV AX, @DATA MOV DS, AX ; YOUR CODE STARTS HERE ; YOUR CODE ENDS HERE MOV AX, 4C00H INT 21H MAIN ENDP END MAIN Collapse :white_tick: 1 Problems : Task 01 a program that takes in 3 digits as input from the user and finds the maximum Sample input: 1st input: 1 2nd input: 2 3rd input: 3 Sample Output: 3 Task 02 Take two digits as input from the user and multiply them. If the result is divisible by 2 and 3 both, print "Divisible". Otherwise, print "Not divisible" Sample input: 1st input: 5 2nd input: 6 Result is 30 Sample Output: Divisible Sample input: 1st input: 5 2nd input: 2 Result is 10 Sample Output: Not divisibleSuppose the implementation of an instruction set architecture uses three classes of instructions, which are called A, B, and C. The total dynamic instruction count is 1 x 10^7 and the processor's clock rate is 2.5 GHz. Details for the three classes are given in the table below: Class CPI % of instructions A 1 20% 50% C 3 30% Complete the following table. Express all answers in scientific notation and round to two decimal places, when needed. Class Instruction Count Number of Clock Cycles х 10^ x 10^ A х 10^ х 10^ x 10^ х 10^ CThe three alternative designs for a computer's central processing unit (CPU) are a general register, a single accumulator, or a stack. Each one has a unique set of benefits and drawbacks. It is up to you to respond, and the response you give might be right or it might be wrong.

- The purpose of this project is to gain a greater understanding of the Intel 32-bit instruction set and understand how a compiler translates C code into assembly language. By compiling the program in unoptimized mode you will hopefully see a fairly clear translation. When running in optimization mode, you will see how well compilers can optimize your code. To compile an unoptimized version use: gcc -Wa,-adhln -g -masm=intel -m32 "Project 2.c" > "Project 2.asm" To compile an optimized version use: gcc -Wa,-adhln -O -masm=intel -m32 "Project 2.c" > "Project 2-o.asm" The -Wa,-adhln option causes gcc to generate intermixed source and assembly code. The -masm=intel option causes gcc to generate assembly code in intel format. The -m32 generates 32-bit code. The -g option generates unoptimized code while -O generates optimized code. The generated code includes quite a few directives that can be ignored. Most of the directives begin with a period (.). There are also a few call…Using C programming language write a program that simulates a variant of the Tiny MachineArchitecture. In this implementation memory (RAM) is split into Instruction Memory (IM) and DataMemory (DM). Your code must implement the basic instruction set architecture (ISA) of the TinyMachine Architecture:1 -> LOAD2 -> ADD3 -> STORE4 -> SUB5 -> IN6 -> OUT7 -> END8 -> JMP9 -> SKIPZEach piece of the architecture must be accurately represented in your code (Instruction Register, ProgramCounter, Memory Address Registers, Instruction Memory, Data Memory, Memory Data Registers, andAccumulator). Data Memory will be represented by an integer array. Your Program Counter will beginpointing to the first instruction of the program. Input SpecificationsYour simulator must run from the command line with a single input file as a parameter to main. This filewill contain a sequence of instructions for your simulator to store in “Instruction Memory” and then runvia the…Write down the machine code of the following assembly instructions for 8088/8086 processor inthe space on the right of each instruction. You can use the handout given to you for assembling theinstructions. AnswerMOV DS, AX; 8ED8XOR DI, DI;MOV DI, 1600;MOV CX, 256;SUB AL, AL;

- As a result, the specific mechanisms by which an instruction obtains its input data are decoupled from the specific means by which any other instruction obtains its input data. Use with a(n): A Synthesizing data sets using procedural descriptions B In contrast to the case of "multiple data, multiple instruction," in which C D stands for "data alone," there is just a single instruction. Many outcomes from a single orderThe CPU design team is designing an instruction set with three classes of instructions. Parameters are given in the following table. Consider a program with 65% ALU instructions, 25% memory access instructions, and 10% control instructions. What is the average CPI for this CPU? Clock Rate 4GHz CPI for ALU Inst. 6 CPI for Memory Inst. 8 CPI for Control Inst. 2Convert the given code fragment to assembly code fragment, using only instructions of the following types. These instructions are generally discussed in class. Here X,Y,Z are any memory locations; R, R1, R2 are any general registers; L is a label in the code (you can use any names as labels, ex. L, L1, L2 etc. ). load X, R //copy contents of memory location X into R. store R, X //Store contents of R into Mem location X cmp R1, R2 //Compute R1-R2 and update condition codes; //throw away result of subtraction. jmp L //Jump to location L in the code. jmpp L //If P bit is 1, Jump to location L in the code add X, R //Add contents of X,R and store result in R; //Also update the condition codes. Be careful about what type of argument is allowed in the instruction (Memory or Register). Ex. the first argument of ADD instruction is memory, not register. Do Not…