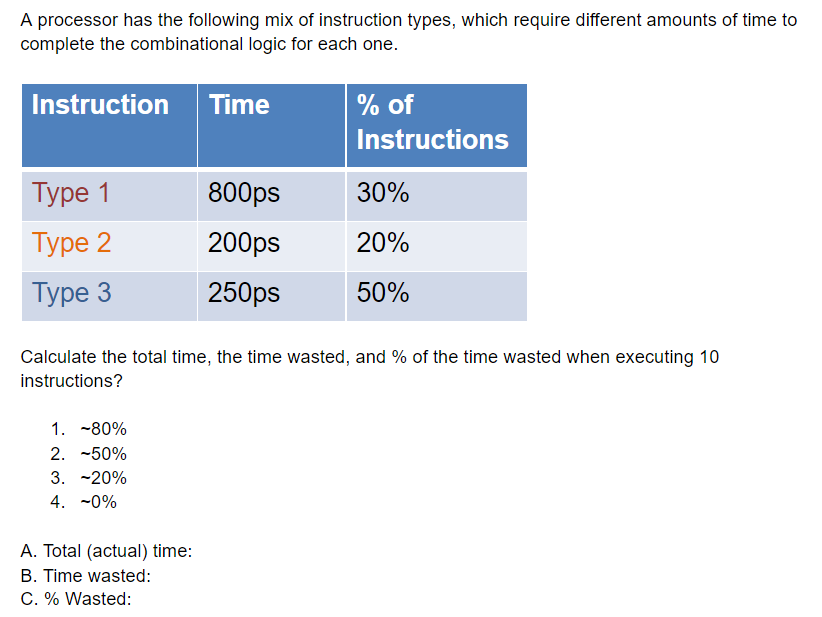

A processor has the following mix of instruction types, which require different amounts of time to complete the combinational logic for each one. Instruction Time % of Instructions Туре 1 800ps 30% Туре 2 200ps 20% Туре 3 250ps 50% Calculate the total time, the time wasted, and % of the time wasted when executing 10 instructions? 1. -80% 2. -50% 3. -20% 4. -0% A. Total (actual) time: B. Time wasted: C. % Wasted:

A processor has the following mix of instruction types, which require different amounts of time to complete the combinational logic for each one. Instruction Time % of Instructions Туре 1 800ps 30% Туре 2 200ps 20% Туре 3 250ps 50% Calculate the total time, the time wasted, and % of the time wasted when executing 10 instructions? 1. -80% 2. -50% 3. -20% 4. -0% A. Total (actual) time: B. Time wasted: C. % Wasted:

Chapter4: Processor Technology And Architecture

Section: Chapter Questions

Problem 15VE: A(n) ________________ instruction always alters the instruction execution sequence. A(n)...

Related questions

Question

Transcribed Image Text:A processor has the following mix of instruction types, which require different amounts of time to

complete the combinational logic for each one.

Instruction Time

% of

Instructions

Туре 1

800ps

30%

Туре 2

200ps

20%

Туре 3

250ps

50%

Calculate the total time, the time wasted, and % of the time wasted when executing 10

instructions?

1. -80%

2. -50%

3. -20%

4. -0%

A. Total (actual) time:

B. Time wasted:

C. % Wasted:

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 2 steps

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning