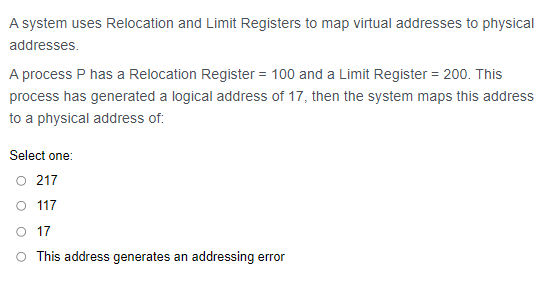

A system uses Relocation and Limit Registers to map virtual addresses to physical addresses. A process P has a Relocation Register = 100 and a Limit Register = 200. This process has generated a logical address of 17, then the system maps this address to a physical address of: Select one: O 217 O 117 O 17 This address generates an addressing error

Q: A paged memory is shared by two processes, p1 and p2. 16 24 15 1 3 -2 9 -3 17 -12 25 -3 18 -16 19 10…

A: Answer

Q: Suppose there is a (non-virtual memory) system that has only 200 Mb of main memory and there are two…

A: Introduction :Given , a non-virtual memory stem , where , size of main memory is = 200 Mb2 process…

Q: A system implements a paged virtual address space for each process using a one-level page table. The…

A: 0x5F4 changed to decimal is 1524. 1524 address occurs on page 1 located at offset 500.Page 0…

Q: Suppose a byte-addressable memory with 4 frames of size 32 bytes each and a paged virtual memory…

A: I will explain it in details,

Q: Assume the operating system for LC-3 has had new service routines added to it. Consider the…

A: q-1) Address used by the above code to access the service routine jump table is x0032 q-2) The…

Q: Consider the following figure about demand paging. The process references page "G" in its logical…

A: Solution is given below :

Q: Suppose that a machine provides instructions that can access memory locations using the one-level…

A: The page fault is the interruption which occurs when the software program attempts to access the…

Q: Question 3 Suppose during an execution of an instruction, the Stack Pointer register had the value…

A: a) The Value Of the Flag Register is Pressed. It means that first the value of the Stack Pointer is…

Q: The jump instruction (j) allows the execution to start from a new address. Opcode (6 bits) Address…

A: Question from jump instruction. jump(X) means we will jump to Address' X' and start execution from…

Q: 16 data lines and a 1- 8086Mp has memory of size: o pins, 14 Byte 2- In 8086Mp, the number of…

A: According to the Bartleby guideline, we are supposed to answer only first 3 fill in the blank…

Q: Suppose we define a service routine starting at memory location x4000. This routine reads in a…

A: Given: As per the policy we can answer single question at time , but i answering 1st and 4th for…

Q: Suppose a process page table contains the entries shown below. Using the format shown in Figure…

A: The process pages are located as follows:

Q: Consider a virtual memory system providing 32 pages for each user program; the size of each page is…

A:

Q: Q2: Suppose that DS-0201h, BX= 300h, and DI- 400h determine the memory address accessed by each of…

A: First, convert all the Hexadecimal numbers into decimal numbers. DS, BX, DI, AL, AX, BI are like…

Q: Draw the mapping cache memory for this system and view the details of the connection between cache…

A: SUMMARY: - Hence, we discussed all the output.

Q: You have a byte-addressable virtual memory system with a two-entry TLB, a 2-way set-associative…

A: Finding the physical address: # of frames in main memory = 4 Frame number bits = log24 = 2 bit

Q: Consider a system with 256Mbytes of main memory with page ize of 4Kbytes. It has a logical address…

A: Here in this question we have given main memory size= 256MB. Page size = 4KB Logical address space=…

Q: space when using the indirect message forwarding paradigm of IPC (or in the kernel). An analogous…

A: The difference between the indirect message passing and shared memory models.

Q: Given The Memory Map and the register values correspond to the state of an 8086 microprocessor. Ss=…

A: Given : Value of SS = 7A20 H Value of SP = 0125 H Value of Stack : 35H 3DH 2BH 67H 5AH

Q: A) Virtual address page 3, offset 7 results in a TLB hit or miss? If TLB hit, what’s the main memory…

A: Here is the solution for the above problem. A) Solution: Virtual page = 4, Here it will result in…

Q: Suppose the page table for a process A currently executing on the processor looks like the…

A: This is a multipart question, we are only allowed to solve 3 parts at a time, I am solving c, d, e…

Q: Suppose that the offset field of a byte-addressed 32-bit paged logical address is 12 bits. Then, a…

A: 1) Byte addressable 32-bit system can accomodate 232 bytes = 4,294,967,296 bytes 2) 12- bit logical…

Q: A computer employs RAM chips of 128 x 8 and ROM chips of 512 x 8. The computer system needs 256…

A: a) 8 RAM chips and 4 ROM chips are reqyuired. Explanation: RAM chip size =256*8 Required memory…

Q: n ? a- 1ACF3H b- 1A32H c- 1AC93H d- 1ACFH

A: The code segment has a value of 1ACFH with 0003H in the instruction pointer what physical address…

Q: Answer only 3 and 4 Suppose memory has 256KB, OS use low address 20KB, there is one program…

A:

Q: Consider a virtual memory system with a 50-bit logical address and a 38-bit physical address.…

A: A virtual memory system with a 50-bit logical address and a 38-bit physical address.Suppose that the…

Q: Idress. process P is associated with a Base Register = 200 and a Limit Register = 100 ocess P…

A: Here the base register is 200 The value of limit register is 100 > logical address. Thus no…

Q: 1. The hypothetical machine of figure 3.4 also has two I/O instructions: 0011= Load AC fro I/O 0111=…

A: Given:

Q: Given a process with address space of size 32 bytes and page size of 8 bytes, if the CPU asks to…

A:

Q: Il- Consider a virtual memory system with the following properties: • 42-bit virtual byte address •…

A:

Q: Suppose two threads T1 and T2 are running concurrently in the same process with a single CPU.…

A: Two threads T1 and T2 are running concurrently in the same process with a single CPU. Suppose T1…

Q: Consider a rtual memory system with the following properties! • 42-bit virtual byte address • 32 KB…

A: Given Data : Virtual address bits = 42 Page size = 32KB Physical address bits = 36 Valid bit = 1…

Q: When a Page Fault is encountered during a Virtual Address translation to Physical Address, either…

A: When a page fault occur , exception is raised by hardware when a running program accesses a memory…

Q: A system implements a paged virtual address space for each process using a one-level page table. The…

A: The virtual address space is =16MB(220.24) = >24 address lines are required there = >24…

Q: Suppose that a machine provides instructions that can access memory locations using the one-level…

A: The answer is given below step:

Q: A direct mapping cache memory of 64 line, main memory consists of 4K block of word/ Show the format…

A: It is defined as a special very high-speed memory. It is used to speed up and synchronizing with…

Q: You have a byte-addressable virtual memory system with a two-entry TLB, a 2-way set-associative…

A: There are seven bits of the virtual address and six bits of the physical address. The given virtual…

Q: A computer with 32 bits virtual address uses a two-level page table. Virtual addresses are split…

A: GIVEN: A computer with 32 bits virtual address uses a two-level page table. Virtual addresses are…

Q: 1. Assume that 8086 Microprocessor segment registers are DS: 1000H CS: 2000H 2- Which of the…

A: Given:

Q: Consider a virtual memory system with a 50-bit logical address and a 38-bit physical address.…

A: A) Total number of pages = virtual address size/ page size = 250/214 = 236 or 64 G pages

Q: A system implements a paged virtual address space for each process using a one-level page table. The…

A: Page Size = 1024 Bytes = 1KBPhysical Memory = 2MBMaximum Virtual Address Space = 16MB

Q: Suppose we define a service routine starting at memory location x4000. This routine reads in a…

A: Given: I am answering the 1st and last question as per the bartlebey policy we can answer single…

Q: Consider a system with 16-bit virtual addresses, 256 byte pages, and 4 byte page table entries. The…

A: PTE's per process = 216/28=28 PTE's per page = 28/22 = 26.

Q: Given a process with address space of size 32 bytes and page size of 8 bytes, if the CPU asks to…

A: Actually. OS is a system software which manages computer hardware and software.

Q: A system implements a paged virtual address space for each process using a one-level page table. The…

A: The maximum number of entries in a page table is computed as follows, Maximum number of entries in a…

Q: A system implements a paged virtual address space for each process using a one-level page table. The…

A: Note: - As per the guidelines we can only answer a maximum of three subparts. Please resubmit the…

Q: size is 1024 bytes and the maximum physical memory size of the machine is 2 megabytes. Assuming two…

A: 3. Number of bits in virtual address = log(virtual address size) = log(maximum size of process) =…

Q: A system implements a paged virtual address space for each process using a one-level page table. The…

A: Physical address: These are hardware address to mapped the physical memory. Virtual address: These…

Q: 25. A system implements a paged virtual address space for each process using a one-level page table.…

A: Given Data : Page size = 1024 bytes Physical address space = 2MB Virtual address space = 16MB

Q: Consider two word wide unsigned integers where one is stored at the physical memory address…

A: Given that, The two word wide unsigned integers where one is stored at the physical memory address…

Step by step

Solved in 2 steps

- Processor R is a 64-bit RISC processor with a 2 GHz clock rate. The average instruction requires one cycle to complete, assuming zero wait state memory accesses. Processor C is a CISC processor with a 1.8 GHz clock rate. The average simple instruction requires one cycle to complete, assuming zero wait state memory accesses. The average complex instruction requires two cycles to complete, assuming zero wait state memory accesses. Processor R can’t directly implement the complex processing instructions of Processor C. Executing an equivalent set of simple instructions requires an average of three cycles to complete, assuming zero wait state memory accesses. Program S contains nothing but simple instructions. Program C executes 70% simple instructions and 30% complex instructions. Which processor will execute program S more quickly? Which processor will execute program C more quickly? At what percentage of complex instructions will the performance of the two processors be equal?A system implements a paged virtual address space for each process using a one-level page table. The maximum size of virtual address space is 16MB. The page table for the running process includes the following valid entries (the → notation indicates that a virtual page maps to the given page frame; that is, it is located in that frame): virtual page 2 → page frame 4 virtual page 1 → page frame 2 virtual page 0 → page frame 1 virtual page 4 → page frame 9 virtual page 3 → page frame 16The page size is 1024 bytes and the maximum physical memory size of the machine is 2MB. How many bits are required for each virtual address?A system implements a paged virtual address space for each process using a one-level page table. The maximum size of virtual address space is 16MB. The page table for the running process includes the following valid entries (the → notation indicates that a virtual page maps to the given page frame; that is, it is located in that frame): virtual page 2 → page frame 4 virtual page 1 → page frame 2 virtual page 0 → page frame 1 virtual page 4 → page frame 9 virtual page 3 → page frame 16The page size is 1024 bytes and the maximum physical memory size of the machine is 2MB.Q.) Which virtual address will translate to physical address 0x400?

- A system implements a paged virtual address space for each process using a one-level page table. The maximum size of virtual address space is 16MB. The page table for the running process includes the following valid entries (the → notation indicates that a virtual page maps to the given page frame; that is, it is located in that frame): virtual page 2 → page frame 4 virtual page 1 → page frame 2 virtual page 0 → page frame 1 virtual page 4 → page frame 9 virtual page 3 → page frame 16The page size is 1024 bytes and the maximum physical memory size of the machine is 2MB.Q.)To which physical address will the virtual address 0x5F4 translate?A system implements a paged virtual address space for each process using a one-level page table. The maximum size of virtual address space is 16MB. The page table for the running process includes the following valid entries (the → notation indicates that a virtual page maps to the given page frame; that is, it is located in that frame): virtual page 2 → page frame 4 virtual page 1 → page frame 2 virtual page 0 → page frame 1 virtual page 4 → page frame 9 virtual page 3 → page frame 16The page size is 1024 bytes and the maximum physical memory size of the machine is 2MB.Q.)What is the maximum number of entries in a page table?Suppose a computer system uses 16-bit addresses for both its virtual and physical addresses. In addition, assume each page (and frame) has size 256 bytes. 8 bits are used for offset, 8 bits are used for page # and the max number of pages a process can have is 256. e. Translate the following virtual addresses to physical addresses, and show how you obtain the answers. (Hint: You do not need to convert hexadecimal numbers to decimal ones.) 0x0389 0xDF78 0x0245 0x8012 f) Now, suppose that the OS uses a two-level page table. Draw the page table. (Assume that frames 7 through 221 are free, so you can allocate space for the page table there.) In addition, suppose that the page-table directory storage comprises a whole number of consecutive full frames. (For examples: if the directory entry is 2 bytes, the entry’s storage comprises 1 frame; if the directory entry is 260 bytes, the entry’s storage comprises 2 consecutive frames.) g)What is the size of the two-level page table…

- Will upvote! Find the memory address of the next instruction executed by the microprocessor, when operated in the real mode, for the following CS:IP and 80286 register combinations: a. DS=2F2E & DX=9D64 b. CS=9F7A & IP=AB27 c. ES=DE21 & DI=D75F d. SS=FF5C & BP=92B8 e. DS=DC67 & CX=2FE8a) A system implements a paged virtual address space for a process using a one-level page table.The maximum size of an address space of process is 16 megabytes.The page table for the running process includes the following entries:Page Number Frame Number 0 4 1 8 2 16 3 17 4 9 The page size is 1024 bytes and the maximum physical memory size of the machine is 2megabytes. Assuming two bits for protection and reference etc.1) How many bits are required for each page table entry?2) What is the maximum number of entries in a page table?3) How many bits are there in a virtual address?4) To which physical address will the virtual address 1524 translate to?Suppose we have a system with 8-byte words and a cache with 32-byte blocks connected directly to memory. The cache has a hit time of 10 ns. The bus to memory is 8 bytes wide, requesting a word from memory takes 100 ns (total, aka round trip time), and memory bus transactions are serialized (not pipelined). The baseline cache requests each word from memory sequentially on a miss, and waits to respond to the CPU until miss repair is fully complete. Consider a workload with poor locality, with a cache hit rate of only 20%. Show your work. (a) What is the AAT speedup of early restart over baseline? Assume a uniform distribution of accesses to each word in a block (25% chance of each). This means that 25% of misses are for word 1 in a block, 25% for word 2, 25% for word 3, and 25% for word 4. (b) What is the AAT speedup over baseline of early restart if the distribution of accesses to each word in a block is 5%, 15%, 30%, and 50%, respectively? (c) What is the AAT speedup over baseline with…

- In this problem, you will explore processor frequency in the context of the speed of light.Suppose you have overclocked a processor to 8,722.78MHz. This processor can execute one instruction per cycle. Further let us suppose that the system is accessing a magnetic disk (HD) with an access time of 11ms. 1. Suppose that you are designing the machine architecture and want to guarantee the CPU can obtain data from memory within 4 CPU cycles. Given that the address has to travel from the CPU to the memory unit (MMU) and that the data has to travel from memory to the CPU, what is the maximum distance between CPU and the MMU if the signal on the memory bus propagates at 75% of the speed of light?In this exercise, we examine in detail how much an instruction is executed in a single-cycle Datapath. The problem refers to a clock cycle in which the processor fetches the following instruction word: 1010 1100 0110 0010 0000 0000 0001 0100. Assume that data memory is all zeros and that the processor's registers have the following values at the beginning of the cycle in which of the instruction word is fetched: (See image attached) What is the new PC address after this instruction is executed? Highlight the path through which this value is determined?Suppose a given processor has access to two levels of memory. Level 1 contains 1000 words and has an access time of 0.01 μs; level 2 contains 100,000 words and has an access time of 0.1 μs. Assume that if a word to be accessed is in level 1, then the processor accesses it directly. If it is in level 2, then the word is first transferred to level 1 and then accessed by the processor. For simplicity, ignore the time required for the processor to determine whether the word is in level 1 or level 2. Suppose 95% of the memory accesses are found in level 1, define the hit ratio (H) and find the average access time.