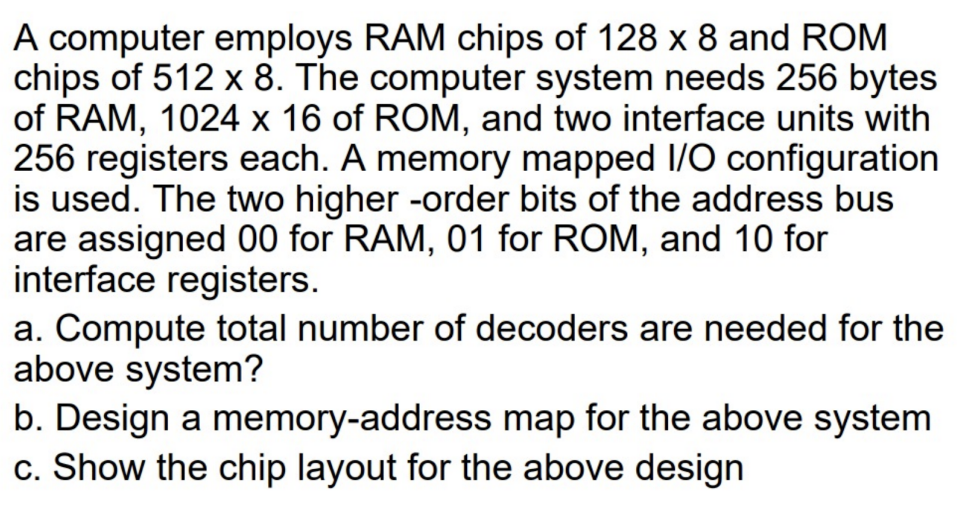

A computer employs RAM chips of 128 x 8 and ROM chips of 512 x 8. The computer system needs 256 bytes of RAM, 1024 x 16 of ROM, and two interface units with 256 registers each. A memory mapped I/O configuration is used. The two higher -order bits of the address bus are assigned 00 for RAM, 01 for ROM, and 10 for interface registers. a. Compute total number of decoders are needed for the above system?

A computer employs RAM chips of 128 x 8 and ROM chips of 512 x 8. The computer system needs 256 bytes of RAM, 1024 x 16 of ROM, and two interface units with 256 registers each. A memory mapped I/O configuration is used. The two higher -order bits of the address bus are assigned 00 for RAM, 01 for ROM, and 10 for interface registers. a. Compute total number of decoders are needed for the above system?

C++ for Engineers and Scientists

4th Edition

ISBN:9781133187844

Author:Bronson, Gary J.

Publisher:Bronson, Gary J.

Chapter2: Problem Solving Using C++using

Section2.3: Data Types

Problem 9E: (Practice) Although the total number of bytes varies from computer to computer, memory sizes of...

Related questions

Question

Transcribed Image Text:A computer employs RAM chips of 128 x 8 and ROM

chips of 512 x 8. The computer system needs 256 bytes

of RAM, 1024 x 16 of ROM, and two interface units with

256 registers each. A memory mapped I/O configuration

is used. The two higher -order bits of the address bus

are assigned 00 for RAM, 01 for ROM, and 10 for

interface registers.

a. Compute total number of decoders are needed for the

above system?

b. Design a memory-address map for the above system

c. Show the chip layout for the above design

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 2 steps with 1 images

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

C++ for Engineers and Scientists

Computer Science

ISBN:

9781133187844

Author:

Bronson, Gary J.

Publisher:

Course Technology Ptr

C++ for Engineers and Scientists

Computer Science

ISBN:

9781133187844

Author:

Bronson, Gary J.

Publisher:

Course Technology Ptr