Consider a 32-bit processor which supports 70 instructions. Each instruction is 32 bit long and has 4 fields namely opcode, two register identifiers and an immediate operand of unsigned integer type. Maximum value of the immediate operand that can be supported by the processor is 8191. How many registers the processor has?

Q: In a computer instruction format, the instruction length is 10 bits and the size of anaddress field…

A: Solution: Given an instruction format with instruction length of 10 bits and size of address filed…

Q: Assuming that we have architecture with instructions that have at least one operand as a machine…

A: Compiler which refers to the special programs that are able to translate the programming languages…

Q: I want all staps for Consider a computer which has a memory which is capable of storing 4096 K words…

A: GIVEN:

Q: Let's assume that there are three processors, Pa, Pb, and Pc, like below. You can assume 1-way…

A: Instructions per second (IPS) = Clock rate / CPI

Q: Question: Suppose a program of 600 instructions runs on a 2 GHz processor. The frequency of…

A: When frequency of instruction and clock cycles counts per instruction is given, then average Clocks…

Q: Consider a computer system with DMA support. The DMA module is transferring a 1-byte character in…

A: Processor speed = 4 MHz 1- byte character in one CPU cycle. 1% of CPU cycle are used for DMA.

Q: Question 2: Consider the following assembly language program and show the stack pointer and register…

A: Because EQU 0F000H therefore stack pointer starts with an address < 0F000H. Initial stack pointer…

Q: Suppose gaming consoles PlayStation 5 and Xbox Series X use different implementations of AMD's Zen…

A: As far bartleby guidelines, I answered only sub questions in first "1" in the given question 1.…

Q: A computer consists of a processor and an I/O device D connected to main memory M via a shared bus…

A: It is given that on a normal a guidance requires 6 cycles and the CPU is occupied 95% of the time in…

Q: Consider a 32-bit processor which supports 30 instructions. Each instruction is 32 bit long and has…

A: The instruction format is Opcode register register operand

Q: In the von Neumann model, the contents of a memory location can also be an instruction. If the…

A: The solution for the above given question is given below:

Q: We have the following statistics for two processors P1 and P2. The two processors have the same…

A: CPI is Clocks per instructions, It is the number of computer clock speed cycles that occur while a…

Q: Consider three different processors P1, P2, and P3 executing the same instruction set. P1 has a 4…

A: Given data: Processor Name Clock Rate CPI P1 4 GHz 1.5 P2 3 GHz 1.0 P3 1.3 GHz 2.2

Q: Consider a processor implementation, P1 of some RISC (MIPS or risc-v) instruction set architecture…

A: Answers Part a) The instruction class Ld/St has CPI(1)=4 and Frequency1= 30%=0.3 Let the instruction…

Q: .CLO2.3: Consider the instruction formats of the basic computer given in class. For the following…

A: please see the next step for solution

Q: Consider two different implementations of the same instruction set architecture. The instructions…

A: Given, =>Two different implementations of same instruction set architecture. Processor Class A…

Q: Consider that the processor fetches the following instruction word: 00010001000101011111111111110001…

A: Given instruction word is 00010001000101011111111111110001 In any binary number, the most…

Q: Assume an 8088 is executing a program in which the probability of a program jump is 0.1. For…

A:

Q: Consider two different instruction sets, Il and 12. Il has 3 classes of instructions, A1, B1 and Cl…

A: The Answer is in Below Steps

Q: onsider a multilevel computer in which levels are vertically stacked, with the lowest level being…

A: Answer :

Q: Consider a system with only two types of instructions, A and B. Type A instructions each require 7…

A: Given: Type A instructions each require (CPIA ) = 7 clock cycles Type B instructions each require…

Q: Suppose a program takes 1 million instruction on a processor having frequency 2 MHz. 50 % of…

A: Lets see the solution.

Q: Show how the following connections through the network are achieved (explain how each switch must be…

A: The switches will be referred as 1A, 2B and so on. The connections are made as follows: i) P0 → M2…

Q: n a computer instruction format, the instruction length is 12 bits and the size of an address field…

A: The instruction length is 12 bits and the size of the address field is 4 bits. The total number of…

Q: Suppose a RISC machine uses overlapping register windows for passing parameters between procedures.…

A: Registers available for use by output parameters: It is given that, The total number of registers…

Q: Two processors A and B have clock rate of 700 MHz and 900 MHz respectively. Suppose A can execute an…

A: In this calculate execution time for both processor ..which ever will take less time..that will be…

Q: n this exercise, we examine in detail how much an instruction is executed in a single-cycle…

A: According to the information given:- Instruction word: 1010 1100 0110 0010 0000 0000 0001 0100.…

Q: Consider a 32-bit processor which supports 30 instructions. Each instruction is 32 bit long and has…

A: Lets discuss the solution in the next steps

Q: Consider the processor of a supercomputer which can support a maximum memory of 128 TB. Assume that…

A: Here we have given solution by applying the formula

Q: Suppose the implementation of an instruction set architecture uses two classes of instructi called A…

A: It is given that: total dynamic instruction count = 3 x 106 Processor's clock rate = 3.2 GHz…

Q: Let us consider a memory that includes two instructions. First instruction is located at memory…

A: CLICK HERE TO GET MORE FREE SOLUTIONS :: Solution :: // C program for the above approach…

Q: You have been contrated to design a memory system for a computer. Assuming the processor has 32…

A: Given: Address line = 32 determine the number of 32 MB memories that can be placed (without…

Q: Consider a processor that contains eight 16-bit registers. (Part A) Design a complete Register file…

A: This register file permits coincidental reading two registers and write in one register properly…

Q: A 32-bit microprocessor with the same bus cycle as a 16-bit microprocessor is an example of this. If…

A: This kind of computer processor has all of its logic and control on one integrated circuit, or a…

Q: Suppose a processor of Harvard architecture has 4 MB instruction memory and 32 MB data memory. If…

A: solution

Q: o Consider the execution of a program of 15,000 instructions by a linear pipeline processor with a…

A: Solution : Given information : Number of instructions (n) = 15000 Frequency (f) = 25 MHz Number of…

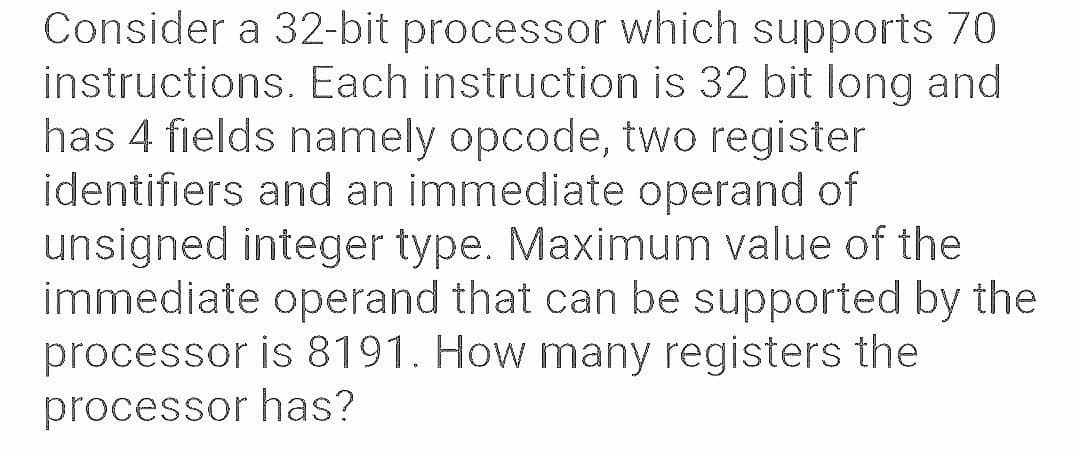

Q: Consider a 32-bit processor which supports 70 instructions. Each instruction is 32 bit long and has…

A:

Q: A computer consists of a processor and an I/O device D connected to main memory M via a shared bus…

A: Given that, on an average, six cycles are required by the instruction.

Q: Consider a computer system that utilizes a 3.6GHZ processor, with 1GB RAM and 17ns memory access…

A: The Answer is

Q: Suppose a RISC machine uses overlapping register windows for passing parameters between procedures.…

A: Registers available for use by output parameters: It is given that, The total number of registers…

Q: Questions 7-8: program is running on a 4 GHz processor. The executed program consists of 2,00,000…

A: The answer is given in the image below

Q: Consider two different implementations, I1 and 12, of the same instruction set. There are three…

A: The answer is in step 2:

Q: Consider computing the overall CPI for a machine Z for which the following performance measures were…

A: Computer Per Instruction: CPI or Computer Per Instruction gives the average number of the cycles of…

Q: Consider two different implementations of the same instruction set architecture. The instructions…

A: On processor P1: Total CPI = 0.1*2 + 0.2*3 + 0.5*4 + 0.2*4 = 0.2 + 0.6 + 2 + 0.8 = 3.6 Total # of…

Q: Consider a 32-bit processor which supports 70 instructions. Each instruction is 32 bit long and has…

A: The Answer is Below Step:-

Q: Consider a CPU that implements a single instruction fetch–decode–execute–write- back pipeline for…

A: As computer systems evolve, greater performance can be achieved by taking advantage of improvements…

Q: Consider the hypothetical processor which has 256 words memory. A 19 bits instruction is placed in 1…

A: The Answer is in below step

Q: Consider two different implementations, M1 and M2, of the same instruction set. There are three…

A: The given data is following- Clock rate for M1 is 2.0 GHz which is equal to 2 × 10^9 Hz. 0 GHz = 2…

Q: 2- Consider two machines with two different instruction sets. Machine A has a 2 GHz clock and…

A:

Trending now

This is a popular solution!

Step by step

Solved in 2 steps

- Take the multiprocessor with 30 processors, each processor is capable od max2Gflops. What is the maximum capability of the multiprocessor for the execution of anapplication that has 5% sequential code?Computer Science 1 .Consider the task of doubling all the elements of a 8192 element vector, which might be done on a SISD machine by the following code. Suppose each iteration of the loop requires 20 clock cycles - so the whole process needs 163,840 clocks. for (int i = 0; i < 8192; i ++) x[i] *= 2.0; Now suppose, instead, that the process is done on a pipelined processor having a single pipeline that supports memory to memory vector operations. Assume that each computation (fetch x[i], double it, store result) still takes 20 clock cycles, but that the pipeline, once full, can produce one result each cycle. How many clock cycles total will be needed for this case?Computer Architecture (Already submit this question, but I think I got wrong solution) Consider a computer that has a number of registers such that the three registers R0 =1500, R1 = 4500, and R2 = 1000 Show the effective address of memory and the registers’ contents in each of the following instructions 1. ADD (R1), R2 2. MOVE 500(R0), R2 3. ADD (40), R1 4. SUBTRACT (5000), R2 5. ADD #30, R2

- Considertwodifferentimplementationsofthesameinstruction set architecture. The instructions can be divided into four classes according to their CPI (class A, B, C, and D). P1 with a clock rate of 2.5 GHz and CPIs of 1, 2, 3, and 3, and P2 with a clock rate of 3 GHz and CPIs of 2, 2, 2, and 2. Given a program with a dynamic instruction count of 1.0E6 instructions divided into classes as follows: 10% class A, 20% class B, 50% class C, and 20% class D, which implementation is faster? a. WhatistheglobalCPIforeachimplementation?Suppose the implementation of an instruction set architecture uses three classes of instructions, which are called A, B, and C. The total dynamic instruction count is 1 x 10^7 and the processor's clock rate is 2.5 GHz. Details for the three classes are given in the table below: Class CPI % of instructions A 1 20% 50% C 3 30% Complete the following table. Express all answers in scientific notation and round to two decimal places, when needed. Class Instruction Count Number of Clock Cycles х 10^ x 10^ A х 10^ х 10^ x 10^ х 10^ CFollow this steps. Have to Consider two different implementations, M1 and M2, of the same instruction set. There arethree classes of instructions (A, B, and C) in the instruction set. M1 has a clock rate of 2.0GHz and M2has a clock rate of 2.5GHz. The average number of cycles for each instruction class and their frequencies(for a typical program) are as follows:Instruction Class M1-Cycles/InstructionClass M2 -Cycles/InstructionClasss FrequencyA 1 2 60%B 3 2 30%C 4 3 10%(a) Calculate the average CPI for each machine, M1, and M2.(b) Calculate the average MIPS ratings for each machine, M1 and M2.(c) Which machine has a smaller MIPS rating? Which individual instruction class CPI do you needto change, and by how much, to have this machine have the same or better performance as themachine with the higher MIPS rating (you can only change the CPI for one of the instructionclasses on the slower machine)?.

- A 32-bit computer has 32 registers, and a memory addressed by bytes with two cycles for reading and writing operations. Consider the instruction ADD, R1, addr. This instruction adds the value stored in R1 to the value stored in the memory address addr, and stores the result in the register R1. a) Show a possible format for this instruction, having into account that the computer has 100 machine instructions and the addresses are represented using 32 bits. b) Indicate the elemental operations and control signals needed to execute the previous instruction.2. Suppose we have two implementations of the same instruction set architecture.Computer A has a clock cycle time of 250 ps and a CPI of 2.0 for some programand computer B has a clock cycle time of 500 ps and a CPI of 1.2 for the sameprogram. Which computer is faster for this program and by how much?Consider a machine with three instruction classes and CPI measurements as follows: Instruction class CPI of the instruction class A 2 B 5 C 7 Suppose that we measured the code for a given program in two different compilers and obtained the following data: Code sequence Instruction counts (in millions) A B C 1 15 5 3 2 25 2 2 Assume that the machine’s clock rate is 500 MHz. Which code sequence will execute faster according to MIPS? How much according to execution time of each code sequence?

- Consider a CPU that implements a single instruction fetch–decode–execute–write- back pipeline for scalar processing. The execution unit of this pipeline assumes that the execution stage requires one step. Describe, and show in diagram form, what happens when an instruction that requires one execution step follows one that requires four execution steps.Please,Consider two different implementations, M1 and M2, of the same instruction set. There arethree classes of instructions (A, B, and C) in the instruction set. M1 has a clock rate of 2.0GHz and M2has a clock rate of 2.5GHz. The average number of cycles for each instruction class and their frequencies(for a typical program) are as follows:Instruction Class M1-Cycles/InstructionClass M2 -Cycles/InstructionClasss FrequencyA 1 2 60%B 3 2 30%C 4 3 10%(a) Calculate the average CPI for each machine, M1, and M2.(b) Calculate the average MIPS ratings for each machine, M1 and M2.(c) Which machine has a smaller MIPS rating? Which individual instruction class CPI do you needto change, and by how much, to have this machine have the same or better performance as themachine with the higher MIPS rating (you can only change the CPI for one of the instructionclasses on the slower machine)?.Consider two different implementations of the same instruction set architecture.The instructions can be divided into four classes according to their CPI (classA, B, C, and D). P1 with a clock rate of 2.5 GHz and CPIs of 2, 3, 4, and 4, andP2 with a clock rate of 3 GHz and CPIs of 2, 2, 3, and 1. Given a program witha dynamic instruction count of 1.0E6 instructions divided into classes asfollows: 10% class A, 20% class B, 50% class C, and 20% class D, whichimplementation is faster?