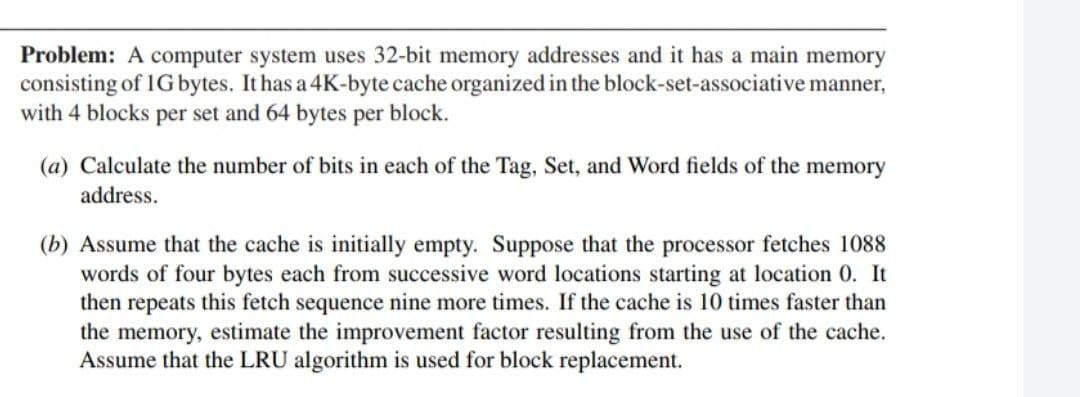

Problem: A computer system uses 32-bit memory addresses and it has a main memory consisting of 1G bytes. It has a 4K-byte cache organized in the block-set-associative manner, vith 4 blocks per set and 64 bytes per block. (a) Calculate the number of bits in each of the Tag, Set, and Word fields of the memory address. (b) Assume that the cache is initially empty. Suppose that the processor fetches 1088 words of four bytes each from successive word locations starting at location 0. It then repeats this fetch sequence nine more times. If the cache is 10 times faster than the memory, estimate the improvement factor resulting from the use of the cache. Assume that the LRU algorithm is used for block replacement.

Problem: A computer system uses 32-bit memory addresses and it has a main memory consisting of 1G bytes. It has a 4K-byte cache organized in the block-set-associative manner, vith 4 blocks per set and 64 bytes per block. (a) Calculate the number of bits in each of the Tag, Set, and Word fields of the memory address. (b) Assume that the cache is initially empty. Suppose that the processor fetches 1088 words of four bytes each from successive word locations starting at location 0. It then repeats this fetch sequence nine more times. If the cache is 10 times faster than the memory, estimate the improvement factor resulting from the use of the cache. Assume that the LRU algorithm is used for block replacement.

Chapter4: Processor Technology And Architecture

Section: Chapter Questions

Problem 2PE: If a microprocessor has a cycle time of 0.5 nanoseconds, what’s the processor clock rate? If the...

Related questions

Question

Answer if you had knowledge else I dislike the answer. Do fast. Don't reject else you can skip it. I also found same question on internet but it's answer is wrong.

Transcribed Image Text:Problem: A computer system uses 32-bit memory addresses and it has a main memory

consisting of 1G bytes. It has a 4K-byte cache organized in the block-set-associative manner,

with 4 blocks per set and 64 bytes per block.

(a) Calculate the number of bits in each of the Tag, Set, and Word fields of the memory

address.

(b) Assume that the cache is initially empty. Suppose that the processor fetches 1088

words of four bytes each from successive word locations starting at location 0. It

then repeats this fetch sequence nine more times. If the cache is 10 times faster than

the memory, estimate the improvement factor resulting from the use of the cache.

Assume that the LRU algorithm is used for block replacement.

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 2 steps

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning