Problem: Suppose that a computer has a processor with two L1 caches, one for instructions and one for data, and an L2 cache. Let t be the access time for the two L1 caches. The miss penalties are approximately 157 for transferring a block from L2 to L1, and 100r for transferring a block from the main memory to L2. For the purpose of this problem, assume that the hit rates are the same for instructions and data and that the hit rates in the L1 and L2 caches are 0.96 and 0.80, respectively. (a) What fraction of accesses miss in both the L1 and L2 caches, thus requiring access to the main memory? (b) What is the average access time as seen by the processor? (c) Suppose that the L2 cache has an ideal hit rate of 1. By what factor would this reduce the average memory access time as seen by the processor? (d) Consider the following change to the memory hierarchy. The L2 cache is removed and the size of the L1 caches is increased so that their miss rate is cut in half. What is the average memory access time as seen by the processor in this case?

Problem: Suppose that a computer has a processor with two L1 caches, one for instructions and one for data, and an L2 cache. Let t be the access time for the two L1 caches. The miss penalties are approximately 157 for transferring a block from L2 to L1, and 100r for transferring a block from the main memory to L2. For the purpose of this problem, assume that the hit rates are the same for instructions and data and that the hit rates in the L1 and L2 caches are 0.96 and 0.80, respectively. (a) What fraction of accesses miss in both the L1 and L2 caches, thus requiring access to the main memory? (b) What is the average access time as seen by the processor? (c) Suppose that the L2 cache has an ideal hit rate of 1. By what factor would this reduce the average memory access time as seen by the processor? (d) Consider the following change to the memory hierarchy. The L2 cache is removed and the size of the L1 caches is increased so that their miss rate is cut in half. What is the average memory access time as seen by the processor in this case?

Operations Research : Applications and Algorithms

4th Edition

ISBN:9780534380588

Author:Wayne L. Winston

Publisher:Wayne L. Winston

Chapter20: Queuing Theory

Section20.10: Exponential Queues In Series And Open Queuing Networks

Problem 11P

Related questions

Question

Assembly language. Pls skip it if you don't have knowledge. Thanks

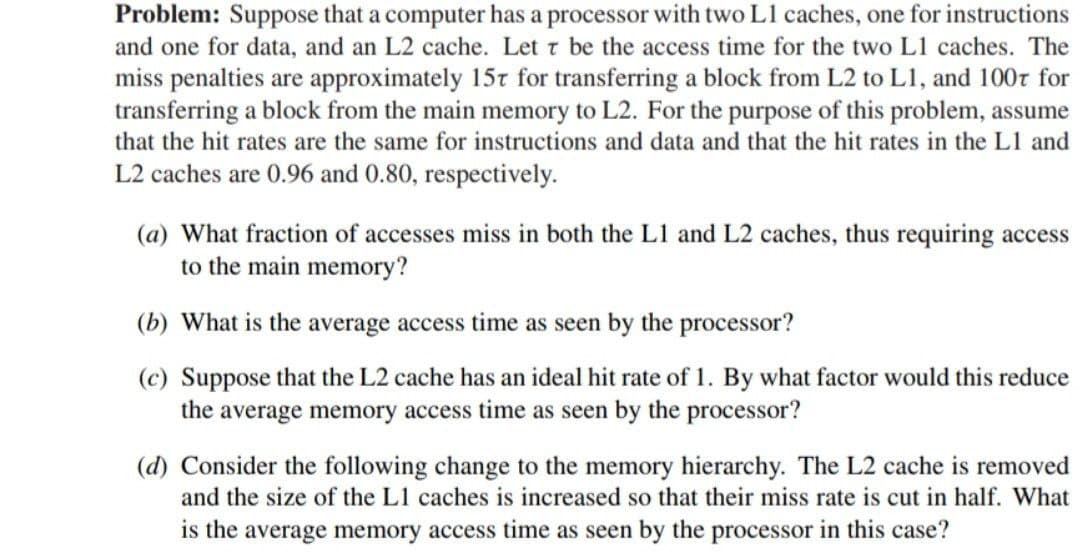

Transcribed Image Text:Problem: Suppose that a computer has a processor with two L1 caches, one for instructions

and one for data, and an L2 cache. Let t be the access time for the two L1 caches. The

miss penalties are approximately 15t for transferring a block from L2 to L1, and 100r for

transferring a block from the main memory to L2. For the purpose of this problem, assume

that the hit rates are the same for instructions and data and that the hit rates in the L1 and

L2 caches are 0.96 and 0.80, respectively.

(a) What fraction of accesses miss in both the L1 and L2 caches, thus requiring access

to the main memory?

(b) What is the average access time as seen by the processor?

(c) Suppose that the L2 cache has an ideal hit rate of 1. By what factor would this reduce

the average memory access time as seen by the processor?

(d) Consider the following change to the memory hierarchy. The L2 cache is removed

and the size of the L1 caches is increased so that their miss rate is cut in half. What

is the average memory access time as seen by the processor in this case?

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 2 steps

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

Operations Research : Applications and Algorithms

Computer Science

ISBN:

9780534380588

Author:

Wayne L. Winston

Publisher:

Brooks Cole

Operations Research : Applications and Algorithms

Computer Science

ISBN:

9780534380588

Author:

Wayne L. Winston

Publisher:

Brooks Cole