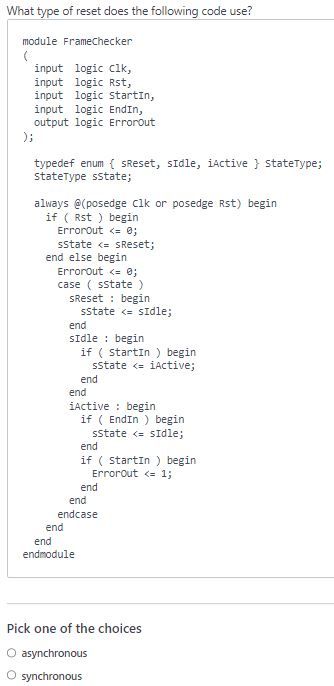

Either an asynchronous or synchronous reset occurs. As soon as the reset signal is asserted, an asynchronous reset begins to operate. As soon as the reset signal is asserted, a synchronous reset begins to operate on the active clock edge.

Regardless of the state of the clock input, asynchronous inputs on such a flip-flop have control over outputs (Q and not-Q). The preset (PRE) and clear inputs are what these are known as (CLR). The flip-flop is driven to a set state by the preset input and to a reset state by the clear input. Synchronous = occurring at the same moment. Asynchronous means not occurring simultaneously. Participants may get quick feedback using synchronous learning. The participants may study at their own speed via asynchronous learning.

Step by stepSolved in 2 steps

- Instructions for both assignments can be found in the picture linked to this post. The programs must be written in c++ and requires that the random number generator be seeded like this program: Program 3.25 // This program demonstrates random numbers. #include <iostream> #include <cstdlib> // For rand and srand #include <ctime> // For the time function using namespace std; int main() { // Get the system time. unsigned seed = time(0); // Seed the random number generator. srand(seed); // Display three random numbers. cout << rand() << endl; cout << rand() << endl; cout << rand() << endl; return 0; }arrow_forwardDraw the hierarchy chart and design the logic for a program that calculates service charges for Hazel's Housecleaning service. The program contains housekeeping, detail loop, and end-of-job modules. The main program declares any needed global variables and constants and calls the other modules. The housekeeping module displays a prompt for and accepts a customer's last name. While the user does not enter ZZZZ for the name, the detail loop accepts the number of bathrooms and the number of other rooms to be cleaned. The service charge is computed as $40 plus $15 for each bathroom and $10 for each of the other rooms. The detail loop also displays the service charge and then prompts the user for the next customer's name. The end-of-job module, which executes after the user enters the sentinel value for the name, displays a message that indicates the program is complete.arrow_forwardZybooks C++ 1.7 LAB: Introduction to data structures labs Step 1: Producing correct output Three commented-out lines of code exist in main(). Uncomment the lines and click the "Run program" button. Verify that the program's output is: 2 + 2 = 4 Unknown function: PrintPlus2 Secret string: "abc" Submit your code for grading. Your submission will pass the "Compare output" test only, achieving 1 of the possible 10 points. Step 2: Inspecting the LabPrinter class Inspect the LabPrinter class implemented in the LabPrinter.h file. Access LabPrinter.h by clicking on the orange arrow next to main.cpp at the top of the coding window. Member functions Print2Plus2() and PrintSecret() print strings using std::cout. Step 3: Implementing CallFunctionNamed() Remove the three uncommented lines from main(). Then implement the CallFunctionNamed() function in main.cpp to handle three cases: If functionName is "Print2Plus2", call printer's Print2Plus2() member function. If functionName is "PrintSecret",…arrow_forward

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science

Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning

Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning

Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education

Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY