Digital Fundamentals

11th Edition

ISBN: 9780133514896

Author: Floyd

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Textbook Question

Chapter 3, Problem 22P

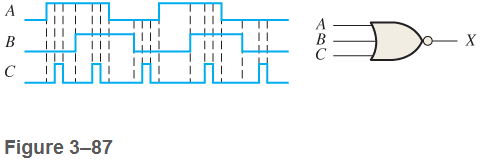

Determine the output waveform in Figure 3-87 and draw the timing diagram.

Expert Solution & Answer

Want to see the full answer?

Check out a sample textbook solution

Students have asked these similar questions

The shift register in Figure(a) has and CLK inputs as shown in part (b). The serial data input (SER) is a 0. The parallel data inputs are D0 = 1, D1 = 0, D2 = 1, and D3 = 0 as shown. Develop the data-output waveform in relation to the inputs.

If the input waveforms are applied to the decoding logic as indicated in Figure 6–76, sketch the output waveform in proper relation to the inputs.

For the circuit in Figure below, complete the timing diagram by showing the Q output (which is initially LOY

Chapter 3 Solutions

Digital Fundamentals

Ch. 3.1 - When a 1 is on the input of an inverter, what is...Ch. 3.1 - An active-HIGH pulse (HIGH level when asserted,...Ch. 3.2 - When is the output of an AND gate HIGH?Ch. 3.2 - When is the output of an AND gate LOW?Ch. 3.2 - Describe the truth table for a 5-input AND gate.Ch. 3.3 - When is the output of an OR gate HIGH?Ch. 3.3 - When is the output of an OR gate LOW?Ch. 3.3 - Describe the truth table for a 3-input OR gate.Ch. 3.4 - When is the output of a NAND gate LOW?Ch. 3.4 - When is the output of a NAND gate HIGH?

Ch. 3.4 - Describe the functional differences between a NAND...Ch. 3.4 - Write the output expression for a NAND gate with...Ch. 3.5 - When is the output of a NOR gate HIGH?Ch. 3.5 - When is the output of a NOR gate LOW?Ch. 3.5 - Describe the functional difference between a NOR...Ch. 3.5 - Write the output expression for a 3-input NOR with...Ch. 3.6 - When is the output of an XOR gate HIGH?Ch. 3.6 - When is the output of an XNOR gate HIGH?Ch. 3.6 - How can you use an XOR gate to detect when two...Ch. 3.7 - List six process technologies used for...Ch. 3.7 - What does the term volatile mean in relation to...Ch. 3.7 - What are two design entry methods for programming...Ch. 3.7 - Prob. 4CUCh. 3.7 - Write a VHDL description of a 3-input NOR gate,Ch. 3.7 - Write a VHDL description of an XOR gate.Ch. 3.8 - How is fixed-function logic different than PLD...Ch. 3.8 - Prob. 2CUCh. 3.8 - Identify the following IC logic designators: LS HC...Ch. 3.8 - Prob. 4CUCh. 3.8 - What does the term hex inverter mean? What does...Ch. 3.8 - A positive pulse is applied to an inverter input....Ch. 3.8 - A certain gate has a propagation delay time of 6...Ch. 3.8 - Prob. 8CUCh. 3.8 - Prob. 9CUCh. 3.8 - Prob. 10CUCh. 3.9 - Prob. 1CUCh. 3.9 - If two different input waveforms are applied to a...Ch. 3.9 - Prob. 3CUCh. 3 - An inverter performs the NOR operation.Ch. 3 - An AND gate can have only two inputsCh. 3 - If any input to an OR is 1, the output is 1.Ch. 3 - If all inputs to an AND gate are 1, the output is...Ch. 3 - A NAND gate has an output that is opposite the...Ch. 3 - A NOR gate can be considered as an OR gate...Ch. 3 - The output of an exclusive-OR is 0 if the inputs...Ch. 3 - Prob. 8TFQCh. 3 - Once programmed, PLD logic can be changed.Ch. 3 - Fan-out is the number of similar gates that a...Ch. 3 - When the input to an inverter is HIGH (1), the...Ch. 3 - An inverter performs an operation known as...Ch. 3 - The output of an AND gate with inputs A, B, and C...Ch. 3 - The output of an OR gate with inputs A, B, and C...Ch. 3 - A pulse is applied to each input of a 2-input NAND...Ch. 3 - A pulse is applied to each input of a 2-input NOR...Ch. 3 - A pulse is applied to each input of an...Ch. 3 - Prob. 8STCh. 3 - The purpose of a programmable link in an AND array...Ch. 3 - The term OTP means open test point one-time...Ch. 3 - Prob. 11STCh. 3 - Prob. 12STCh. 3 - Two ways to enter a logic design using PLD...Ch. 3 - Prob. 14STCh. 3 - In-system programming of a PLD typically utilizes...Ch. 3 - To measure the period of a pulse waveform, you...Ch. 3 - Prob. 17STCh. 3 - The input waveform shown in Figure 3-76 is applied...Ch. 3 - A combination of inverters is shown in Figure...Ch. 3 - If the waveform in Figure 3-76 is applied to point...Ch. 3 - Draw the rectangular outline symbol for a 4-input...Ch. 3 - Determine the output, X, for a 2-input AND gate...Ch. 3 - Repeat problem 5 for the waveforms in Figure 3-79Ch. 3 - The input wave forms applied to a 3-input AND gate...Ch. 3 - The input waveforms applied to a 4-input AND gate...Ch. 3 - Draw the rectangular outline symbol for a 3-input...Ch. 3 - Write the expression for a 5-input OR gate with...Ch. 3 - Determine the output for a 2-input OR gate when...Ch. 3 - Repeat Problem 7 for a 3-input OR gate.Ch. 3 - Repeat Problem 8 for a 4-input OR gate.Ch. 3 - For the five input waveforms in Figure 3-8219,...Ch. 3 - Draw the rectangular outline symbol for a 4-input...Ch. 3 - Show the truth table for a 3-input OR gate.Ch. 3 - For the set of input waveforms in Figure 3-83,...Ch. 3 - Determine the gate output for the input waveforms...Ch. 3 - Determine the output waveform in Figure 3-8513Ch. 3 - As you have learned, the two logic symbols shown...Ch. 3 - Repeat Problem 17 for a 2-input NOR gate.Ch. 3 - Determine the output waveform in Figure 3-87 and...Ch. 3 - Repeat Problem 19 for a 4-input NOR gate.Ch. 3 - The NAND and the negative-OR symbols represent...Ch. 3 - How does an exclusive-OR gate differ from an OR...Ch. 3 - Repeat Problem 17 for an exclusive-OR gate.Ch. 3 - Repeat Problem 17 for an exclusive-NOR gateCh. 3 - Determine the output of an exclusive-OR gate for...Ch. 3 - In the simple programmed AND array with...Ch. 3 - Determine by row and column number which fusible...Ch. 3 - Describe a 4-input AND gate using VHDL.Ch. 3 - Describe a 5-input NOR gate using VHDLCh. 3 - In the comparison of certain logic devices, it is...Ch. 3 - Prob. 34PCh. 3 - Determine tPLHandtPHL from the oscilloscope...Ch. 3 - Prob. 36PCh. 3 - If a logic gate operates on a dc supply voltage of...Ch. 3 - The variable ICCH represents the dc supply current...Ch. 3 - Examine the conditions indicated in Figure 3-92,...Ch. 3 - Determine the faulty gates in Figure 3-93 by...Ch. 3 - Using an oscilloscope, you make the observations...Ch. 3 - Prob. 42PCh. 3 - Every time the ignition switch is turned on in the...Ch. 3 - What failure(s) would you suspect if the output of...Ch. 3 - Modify the frequency counter in Figure 3-16 to...Ch. 3 - Prob. 46PCh. 3 - Design a circuit to fit in the beige block of...Ch. 3 - Modify the logic circuit for the intrusion alarm...Ch. 3 - Further modify the logic circuit from Problem 48...Ch. 3 - Sensors are used to monitor the pressure and the...Ch. 3 - In a certain automated manufacturing process,...Ch. 3 - Open file P03-52. For the specified fault, predict...Ch. 3 - Open file P03-53. For the specified fault, predict...Ch. 3 - Open file P03-54. For the observed behavior...Ch. 3 - Open file P03-55. For the observed behavior...

Additional Engineering Textbook Solutions

Find more solutions based on key concepts

Indexing can clearly be very beneficial. Why should you not create an index for every column of every table of ...

Modern Database Management (12th Edition)

Suppose a is an array of values of type double that is partially filled. The array contains meaningful values i...

Java: An Introduction to Problem Solving and Programming (7th Edition)

The ________ object is assumed to exist and it is not necessary to include it as an object when referring to it...

Web Development and Design Foundations with HTML5 (9th Edition) (What's New in Computer Science)

What does the throw statement do?

Starting Out with Java: Early Objects (6th Edition)

What is an object? What is a control?

Starting Out With Visual Basic (8th Edition)

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Similar questions

- Referring to the circuit in Figure 2(c), construct the timing diagram in Figure 2(d) by showing the Q output (which initially LOW). Consider also the given PRE and CLR Inputs.arrow_forwardDesign the 7 segment display decoder circuit as shown in the truth table belowarrow_forwardDraw the circuit and obtain the truth table of the VHDL module below module SAM(a, b, c, M, S);input a,b,c;output M;output S;wire d,e,f;xor(S,a,b,c);and(d,~a,b);and(e,b,c);and(f,~a,c);or(M,d,e,f);endmodulearrow_forward

- Complete the timing diagram for the following circuit. Assume that the signal delay through the NOR gates is 3 ns, and the delay through the NOT gate is 1 ns.arrow_forwardWrite the working principle, design, circuit diagram and precaution of BCD Seven Segment Decoder Displayarrow_forwardExplain the principle of operation of the Mod-14 asynchronous counter with using the required figures, then draw the timing diagram for the input and output of this counter when the frequency of the input signal is 10KHz.arrow_forward

- In quartus, design a state machine that produces a two-second on-pulse followed by a four-second off-pulse.arrow_forwardIdentify the state diagram operation and find its output sequence for the following input sequence X=0101-1100-101-0000 the circuit accepts input bits from LSB to MSBarrow_forward(a) Design a 2 bit parallel binary adder with Full adders only. (b) The input waveform shown in figure is applied to the above 2 bit parallel adder. Draw the output waveform for sum and output carryarrow_forward

- Create a Minterm expansion and design a digital circuit based off the truth tablearrow_forwarddraw a qpsk complete modulator circuit using circuit components of various types not a block diagram.arrow_forwardGiven the ASM chart in the figure, design the control logic of the system using D Flip-Flops and decoder. Use G1, G2, G3, G4, etc. as flip-flop variables where G1 holds the most significant bit (MSB). Use the state assignments given in the ASM chart.arrow_forward

arrow_back_ios

SEE MORE QUESTIONS

arrow_forward_ios

Recommended textbooks for you

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON

Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON

Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON

C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning

Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Database System Concepts

Computer Science

ISBN:9780078022159

Author:Abraham Silberschatz Professor, Henry F. Korth, S. Sudarshan

Publisher:McGraw-Hill Education

Starting Out with Python (4th Edition)

Computer Science

ISBN:9780134444321

Author:Tony Gaddis

Publisher:PEARSON

Digital Fundamentals (11th Edition)

Computer Science

ISBN:9780132737968

Author:Thomas L. Floyd

Publisher:PEARSON

C How to Program (8th Edition)

Computer Science

ISBN:9780133976892

Author:Paul J. Deitel, Harvey Deitel

Publisher:PEARSON

Database Systems: Design, Implementation, & Manag...

Computer Science

ISBN:9781337627900

Author:Carlos Coronel, Steven Morris

Publisher:Cengage Learning

Programmable Logic Controllers

Computer Science

ISBN:9780073373843

Author:Frank D. Petruzella

Publisher:McGraw-Hill Education

Boolean Algebra - Digital Logic and Logic Families - Industrial Electronics; Author: Ekeeda;https://www.youtube.com/watch?v=u7XnJos-_Hs;License: Standard YouTube License, CC-BY

Boolean Algebra 1 – The Laws of Boolean Algebra; Author: Computer Science;https://www.youtube.com/watch?v=EPJf4owqwdA;License: Standard Youtube License