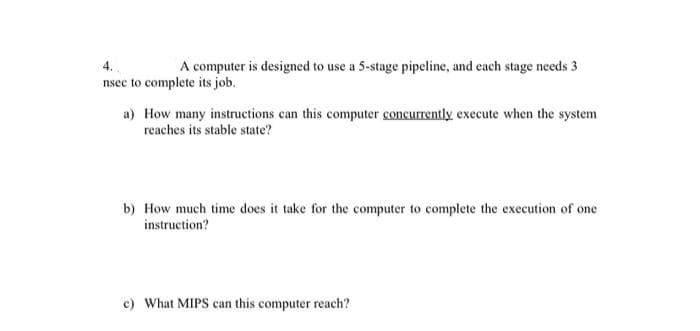

4. A computer is designed to use a 5-stage pipeline, and each stage needs 3 nsec to complete its job. a) How many instructions can this computer concurrently execute when the system reaches its stable state? b) How much time does it take for the computer to complete the execution of one instruction? c) What MIPS can this computer reach?

Q: Suppose that a microprocessor operates at 5MHz. How long does the bus cycle occupy, assuming no wait…

A: Answer 800 ns

Q: b. Consider an ARM CPU that executes its instructions using a simple 3-stage pipeline consisting of…

A: Answer: I have the given answer the brief explanation.

Q: Assume a pipelined processor with five pipeline stages where each stage takes one clock cycle.…

A: Answer: I have given answer in the brief explanation.

Q: Consider a computer system with DMA support. The DMA module is transferring a 1-byte character in…

A: Processor speed = 4 MHz 1- byte character in one CPU cycle. 1% of CPU cycle are used for DMA.

Q: Consider a pipeline that has 5 stages: (1) instruction fetch – 200 ps, (2) instruction decode - 100…

A: Answer is given below-

Q: Segment Execution Activity 2 Segment Name Time (ns) Instruction Fetch & Decode (IF) Operand Fetch…

A: pipeline: Pipelining is a process of arrangement of hardware elements of the CPU such that its…

Q: Consider the unpipelined machine with 10 nano seconds clock cycles. It uses four cycles for ALU…

A: The answer is

Q: A computer consists of a processor and an I/O device D connected to main memory M via a shared bus…

A: It is given that on a normal a guidance requires 6 cycles and the CPU is occupied 95% of the time in…

Q: Suppose on a non-pipelined single-processor machine, you have the following breakdown: alu…

A: (a)Non-pipelined single-processor machineAverage CPI = (0.25*2 + 0.3*10 + 0.15*4 + 0.3*1.5) = 4.55

Q: ) Let us assume that we have a program of 100,000 instructions. Each instruction is independent from…

A: Here, we are going to find out the number of CPU cycles needed to execute the program. In pipeline…

Q: The runtimes of the five stages of executing an instruction in a non-pipelined machine are listed…

A: The above question is solved in step 2:-

Q: Consider a datapath with 6 stages. Operation times/delays associated with each of these 6 stages are…

A: We have 6 different stages with stage delay. And we have to calculate clock period for pipelined and…

Q: a. what is the clock cycle time in a pipelined and non-pipelined processor? b. what is the total…

A: a) what is the clock cycle time in a pipelined and non-pipelined processor? Pipelining: In it, all…

Q: 2) A computer has a pipeline with 3 stages. First stage takes nsec, second stage takes 5 nsec and…

A: Instruction per second machine execution

Q: How many stalls (in terms of the number of stall clock cycles) will the processor experience if it…

A: It is defined as the amount of time between two pulses of an oscillator. Generally speaking, the…

Q: Consider a pipelined system with four stages: IF, ID, EX, WB. Following chart shows the clock cycles…

A: It is defined as a process of executing multiple instructions simultaneously. In pipelining the…

Q: What would be the clock period of a pipelined MIPS architecture with two stages, one comprising…

A: What would be the clock period of a pipelined MIPS architecture with two stages, one comprising…

Q: The runtimes of the five stages of executing an instruction in a non-pipelined machine are listed…

A: Answer A1. Even if one of the two longest pipeline stages (300ps) is split into two pipeline…

Q: Assume a 5-stage pipelined CPU (IF – ID – MU– EX – WR) requires following time for different…

A:

Q: Assume an 8088 is executing a program in which the probability of a program jump is 0.1. For…

A:

Q: a) Determine the number of cycles to execute 175 instructions for non-pipelined processor and…

A: Hi, As per the QnA policy, we are allowed to solve the first three sub-parts of a multipart…

Q: What is the minimum number of clock cycles needed to completely execute n instructions on a…

A: Pipelining is a process of arranging the hardware components in such a way that it can execute…

Q: Consider a pipelined system with four stages: IF, ID, EX, WB. Following chart shows the clock cycles…

A:

Q: If the execution time of pipeline instruction execution is not balanced, what inefficiency must be…

A: Pipelining does not help with one job delay, it helps to get through all the workPipeline level is…

Q: Assume that a lA32 computer has 8 execution stages and you want to execute a programwith 25…

A: Given that, Number of execution stages= 8 Number of instructions= 25

Q: Instead of a single-cycle organization, we can use a multi-cycle organization where each instruction…

A: Clock cycle times and execution times The multi cycle organization has the same clock cycle time as…

Q: Computer Science Suppose for a processor system it takes 35 cycles to push and pop registers onto…

A: Suppose for a processor system it takes 35 cycles to push and pop registers onto the stack and…

Q: How many cycles are required for the pipelined MIPS processor to issue all of the instructions for…

A: 4 + (3 + 4 + 3) X 5 + 3 = 57 clock cycles The number of instructions executed is 1 + (3 X 5) + 1 =…

Q: A wait state(a) terminates a bus cycle(b) halts the processor clock for one period(c) places the…

A: Wait state is the state that keeps the bus signals on hold for the required processor cycles so as…

Q: Assume that individual data path stages have the following latencies: IF ID EX MEM WB 250 ps 200 ps…

A: Answer in step2

Q: A non pipelined processor has a clock cycle of 8.0 ns to execute each instruction. If a 6-stages…

A: Here, we are going to find out the new clock cycle when we implemented a 6-stages pipeline processor…

Q: The following sequence of instructions are executed in the basic 5-stage pipelined processor OR R1,…

A: From the processor accumulate the instruction is called Pipelining. Instructions can be store and…

Q: Suppose an instruction takes 6 cycles to execute in an unpipelined CPU: one cycle to fetch the…

A: Actually, the answer has given below:

Q: A computer consists of a processor and an I/O device D connected to main memory M via a shared bus…

A: Given that, on an average, six cycles are required by the instruction.

Q: Consider the following sequence of instructions: 1. LOAD F4, 16(R2) 2. LOAD F6, 48(R2) 3. MUL F10,…

A: Below is the answer with explanation:

Q: d) Consider I have the following instructions Id addi x11, x12, 5 x12, 16(x11) add x13, x11, x12…

A: In above code we can see that each instruction consist of 3-stage . however, some instruction depend…

Q: Suppose that a CPU always executes the two instructions following a branch instruction, regardless…

A: It can be made fast by using ignore instruction when any branch is busy.

Q: Why is a single instruction in a pipeline datapath not shorter than that in a multi-cycle datapath…

A: The ask is to explain why a single instruction in a pipeline datapath not shorter than that in a…

Q: On an ARM processor, assuming that [N-bit] = 0, [Z-bit] = 0, [C-bit] = 1, [V-bit] = 1, predict…

A: 1)NO The Instruction BLS (Branch on Lower than or Same) condition test is (NOT C OR Z)==1 but the…

Q: Consider the following sequence of instructions: 1. LOAD F4, 16(R2) 2. LOAD F6, 48(R2) B. MUL F10,…

A: Introduction :

Q: Suppose an instruction takes four cycles to execute in a nonpipelined CPU: one cycle to fetch the…

A: Explanation: It speeds up the execution because the four-stage pipelined processor can execute the…

Q: A processor takes 24 cycles to complete an instruction 1 with frequency 4 GHz. The corresponding…

A: Find the required answer with calculation given as below :

Q: a datapath With 6 stages. Operation times/delays associated each öf these 6 stages are shown below:…

A: d) To execute 5 instructions on pipeline implementation: The total time for a pipeline is = 34*50…

Q: Write a single instruction that will load BX from address [E120H] and ES from address [1E22H]

A: For first instruction to move value stored in memory location E120H to BX register using mov…

Q: For questions Q11 and Q12, consider a computer running a program that requires 400 s, with 220 s…

A: Dear Student, To solve this problem we just need to find the time required for executing the program…

Q: Assume the processor is driven by a clock, such that each control step is 4 ns in duration. How long…

A: Given Data : Control Step time = 4ns Read operation time = 12 ns To find : Percentage of time…

Q: A hypothetical processor has 9 stages of a pipeline as shown in the table below. The first row in…

A: Note: As you have asked multiple questions, as per our policy, we will solve the first question for…

Q: Question 9: Consider the timing diagram of Figure 1. Assume that there is only a five-stage pipeline…

A: We are given a Timing Diagram for Instruction Pipeline Operation. Each instructions has 5 stages…

Q: . Consider a pipelined RISC CPU with 11 stages. What is maximum speedup of this CPU over a…

A:

Trending now

This is a popular solution!

Step by step

Solved in 2 steps

- Suppose an instruction takes four cycles to execute in a nonpipelined CPU: one cycle to fetch the instruction, one cycle to decode the instruction, one cycle to perform the ALU operation, and one cycle to store the result. In a CPU with a four-stage pipeline, that instruction still takes four cycles to execute, so how can we say the pipeline speeds up the execution of the program?Assume that a lA32 computer has 8 execution stages and you want to execute a programwith 25 instructions. How fast a pipelined computer will execute the instructions than anon- pipelined computer?Is it still feasible to accomplish pipelined execution even if the time it takes to execute pipeline instructions is not balanced? Where can you perceive the inefficiencies in this situation?

- A hypothetical processor has 9 stages of a pipeline as shown in the table below. The first row in the table below shows the pipeline stage number, second row gives the name of each stage, and third row gives the delay of each stage in Nano-seconds. The name of each stage describes the task performed by it. Each stage takes 1 cycle to execute. This processor stores all the register contents in a compressed fashion. After fetching the operands the operands are first decompressed, and before saving the results in register file, the results are first compressed. a)How many cycles are required to execute one instruction on this pipeline? b)How many cycles are required to execute 19 instructions on this pipeline? Assume that no stall cycles occur during the execution of all instructions. c) Assume that all necessary bypass/forwarding circuitry is implemented in this 9 stage pipeline. How many cycles will the pipeline stall during the execution of below given two instructions? Briefly explain…Yes, even if pipeline instructions take a different amount of time to execute at different times. Where can the problems with this situation be found?If the execution times of the pipeline instructions are not balanced, is pipelined execution still possible? Where do you see the inefficiencies here?

- Can pipelined execution be attained if the times at which individual pipeline instructions run are not equal? Exactly what inefficiency have you noticed?Assume a 3GHz processor executes three classes of instructions(A, B, C).i. Calculate the average CPI for this sequence of program.ii. Calculate the execution time for this sequence of program.iii. If we use a system with four same processors, there will bespeed up by a factor of 4 for classes A and C, but class B willremain unaffected. Calculate the new execution time for thissystem. What is the overall speed up? Class A B C CPI for class 4 2 10 IC in sequence 100 200 300On a modern pipelined computer, how can a computer programme be optimised so that it runs rapidly and consumes little energy?

- What is pipelining in computer architecture, and how does it improve CPU performance? Provide a basic diagram to illustrate a 5-stage pipeline.An operation is considered to have been successfully stopped when the central processing unit (CPU) accepts the interruption and proceeds on to the next job. If the process is already underway, then why is it impossible to halt it? Since the execution and cleaning can wait till we've resolved the problem, there's no reason not to take care of them right now.Suppose that a microprocessor operates at 5MHz. How long does the bus cycle occupy, assuming no wait states are inserted?