Mark each of the following statements as T for true or as F for false? a. Dynamic or clocked logic gates are used to decrease complexity, increase speed, and lower power dissipation. b. If an MOS transistor is off it can still leak current known as Ioff which is the current between drain and source c. A ring oscillator built from CMOS inverters can oscillate if the number of inverters is odd. d. One of the uses of a phase locked loop is to multiply an input clock to a much higher frequency. In a CMOS inverter the dynamic power dissipation increases as the switching frequency increases.

Mark each of the following statements as T for true or as F for false? a. Dynamic or clocked logic gates are used to decrease complexity, increase speed, and lower power dissipation. b. If an MOS transistor is off it can still leak current known as Ioff which is the current between drain and source c. A ring oscillator built from CMOS inverters can oscillate if the number of inverters is odd. d. One of the uses of a phase locked loop is to multiply an input clock to a much higher frequency. In a CMOS inverter the dynamic power dissipation increases as the switching frequency increases.

Chapter22: Sequence Control

Section: Chapter Questions

Problem 6SQ: Draw a symbol for a solid-state logic element AND.

Related questions

Question

Please answer question 1a,1b,1c in the image. With details on how to do it. Also please make handwriting legible and clear to understand.

Thank you.

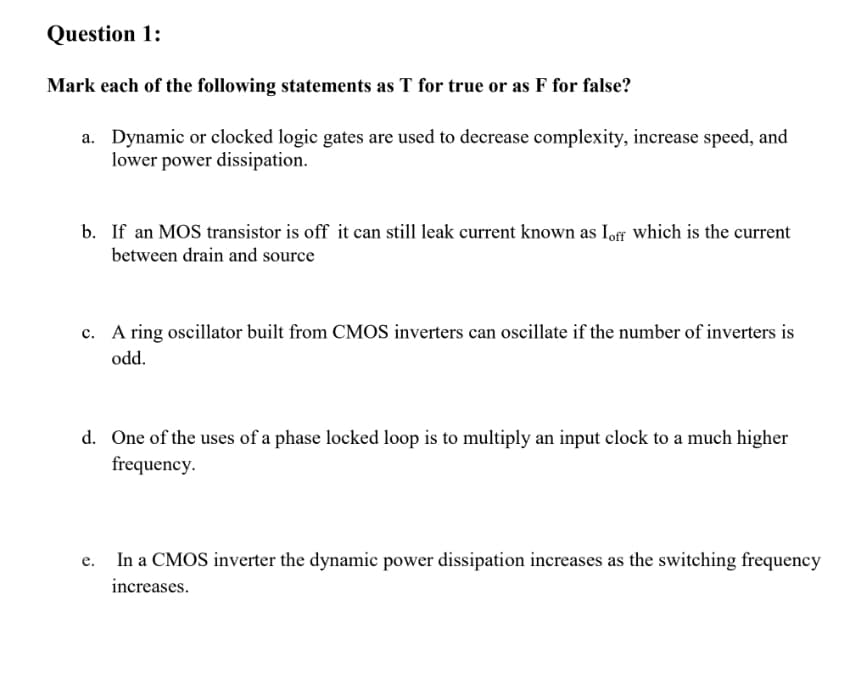

Transcribed Image Text:Question 1:

Mark each of the following statements as T for true or as F for false?

a. Dynamic or clocked logic gates are used to decrease complexity, increase speed, and

lower power dissipation.

b. If an MOS transistor is off it can still leak current known as Iof which is the current

between drain and source

c. A ring oscillator built from CMOS inverters can oscillate if the number of inverters is

odd.

d. One of the uses of a phase locked loop is to multiply an input clock to a much higher

frequency.

In a CMOS inverter the dynamic power dissipation increases as the switching frequency

e.

increases.

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

Step by step

Solved in 3 steps

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, electrical-engineering and related others by exploring similar questions and additional content below.Recommended textbooks for you