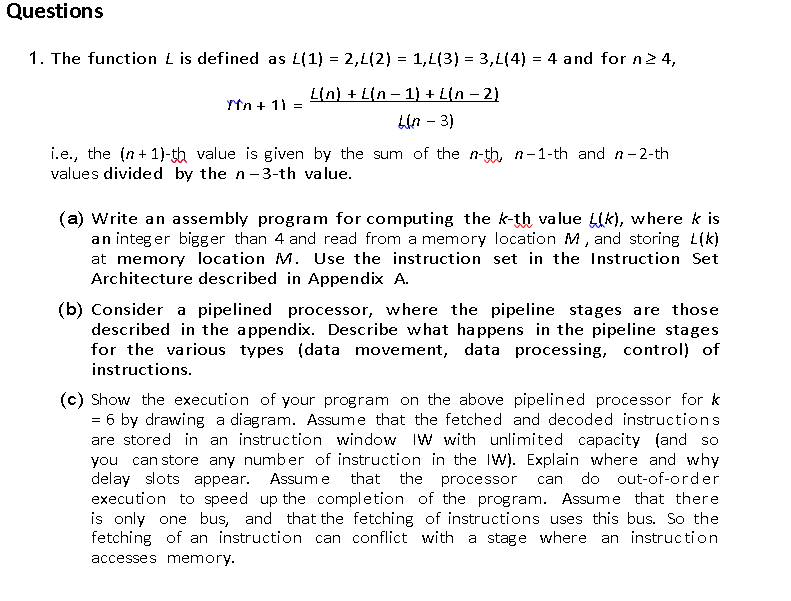

Show the execution of your program on the above pipelined processor for k = 6 by drawing a diagram. Assume that the fetched and decoded instructions are stored in an instruction window IW with unlimited capacity (and so you can store any number of instruction in the IW). Explain where and why delay slots Assume that the processor can do out-of-order execution to speed up the completion of the program. Assume that there is only one bus, and that the fetching of instructions uses this bus. So the fetching of an instruction can conflict with a stage where an instruction accesses memory. A Instruction Set Architecture A.1 Instruction set

Quesion:

- Show the execution of your

program on the above pipelined processor for k = 6 by drawing a diagram. Assume that the fetched and decoded instructions are stored in an instruction window IW with unlimited capacity (and so you can store any number of instruction in the IW). Explain where and why delay slots Assume that the processor can do out-of-order execution to speed up the completion of the program. Assume that there is only one bus, and that the fetching of instructions uses this bus. So the fetching of an instruction can conflict with a stage where an instruction accesses memory.

A Instruction Set Architecture

A.1 Instruction set

We present a list of instructions typical of a RISC (reduced instruction set computer) machine. In data-movement and control instructions, the addresses may be immediate #X, direct (memory) M, indirect (memory) [M], register r, or register indirect [r] addresses. Data-processing instructions use immediate or register addressing. PC is the programme counter and a <- b indicates that the value of b is placed in a.

LOAD a, b a <- b

STOR a, b a <- b

ADD a, b, c a <- b + c

ASH a, b, c a <- (b >>[s] c)

LSH a, b, c a <- (b >>[u] c) BR a PC <- a

|

SUB |

a, |

b, |

c |

a |

<- |

b |

- c |

BEQ |

a, |

b, |

c |

PC |

<- |

a |

if |

b = |

c |

|

MUL |

a, |

b, |

c |

a |

<- |

b |

* c |

BNE |

a, |

b, |

c |

PC |

<- |

a |

if |

not |

b = c |

|

DIV |

a, |

b, |

c |

a |

<- |

b |

/ c |

BLT |

a, |

b, |

c |

PC |

<- |

a |

if |

b < |

c |

|

AND |

a, |

b, |

c |

a |

<- |

b |

& c |

BGT |

a, |

b, |

c |

PC |

<- |

a |

if |

b > |

c |

OR a, b, c a <- b | c

NOT a, b a <- !b

BLE a, b, c PC <- a if b <= c BGE a, b, c PC <- a if b >= c

Note: Here b >>[s] c denotes the arithmetical shift of b to the right by c positions, and

b >>[u] c denotes the logical shift of b to the right by c positions.

A.2 The pipeline

We will use a five-stage pipeline:

- IF (instruction fetch),

- ID (instruction decode),

- RR (register read),

- EX (execute instruction),

- WB (write back result into register).

- Note that for some instructions (e.g., LOAD r, #X) some of the pipeline stages (e.g., RR) are not

A.3 Execution rules

The rules for the execution of instructions are as follows:

- All instructions go through the IF and ID stages

- For data-movement instructions the data transfer between the CPU and main mem- ory happens in the execute stage. (This means that if a data transfer operation is executing, no data can be transferred across the main-memory )

- Immediate addressing for input arguments does not require RR or EX (e.g., LOAD r1, #X).

- Arithmetic and logic instructions need RR, EX and

- Branching operations require RR, EX and WB, unless all operands are immediate, in which case only EX and WB are

- For the instruction LOAD a, b the argument b must be an immediate address or memory location and a must be a

- For the instruction STOR a, b the argument b must be an immediate address or register and a must be a memory

- For each of the remaining instructions the arguments a, b and c must all be registers or immediate

- You may assume for the sake of the questions that the ISA supports floating point arithmetic with no loss of precision

Trending now

This is a popular solution!

Step by step

Solved in 2 steps