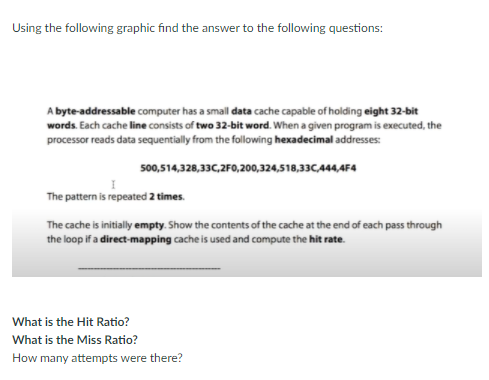

Using the following graphic find the answer to the following questions: A byte-addressable computer has a smal data cache capable of holding eight 32-bit words. Each cache line consists of two 32-bit word. When a given program is executed, the processor reads data sequentially from the following hexadecimal addresses: s00,514,328,33C,2F0,200,324,518,33C444,4F4 The pattern is repeated 2 times. The cache is initiall empty. Show the contents of the cache at the end of each pass through the loop if a direct-mapping cache is used and compute the hit rate. What is the Hit Ratio? What is the Miss Ratio? How many attempts were there?

Using the following graphic find the answer to the following questions: A byte-addressable computer has a smal data cache capable of holding eight 32-bit words. Each cache line consists of two 32-bit word. When a given program is executed, the processor reads data sequentially from the following hexadecimal addresses: s00,514,328,33C,2F0,200,324,518,33C444,4F4 The pattern is repeated 2 times. The cache is initiall empty. Show the contents of the cache at the end of each pass through the loop if a direct-mapping cache is used and compute the hit rate. What is the Hit Ratio? What is the Miss Ratio? How many attempts were there?

Chapter4: Processor Technology And Architecture

Section: Chapter Questions

Problem 2PE: If a microprocessor has a cycle time of 0.5 nanoseconds, what’s the processor clock rate? If the...

Related questions

Question

Please have clear steps thank you

Transcribed Image Text:Using the following graphic find the answer to the following questions:

A byte-addressable computer has a small data cache capable of holding eight 32-bit

words. Each cache line consists of two 32-bit word. When a given program is executed, the

processor reads data sequentially from the following hexadecimal addresses:

500,514,328,33C,2F0,200,324,518,33C444,4F4

The pattern is repeated 2 times.

The cache is initially empty. Show the contents of the cache at the end of each pass through

the loop if a direct-mapping cache is used and compute the hit rate.

What is the Hit Ratio?

What is the Miss Ratio?

How many attempts were there?

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 5 steps with 1 images

Recommended textbooks for you

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning