Suppose we have a system with following properties:

- The memory is byte addressable.

- Memory accesses are to 1-byie wards (not to 4-byte words).

- Addresses arc 13 bits wide.

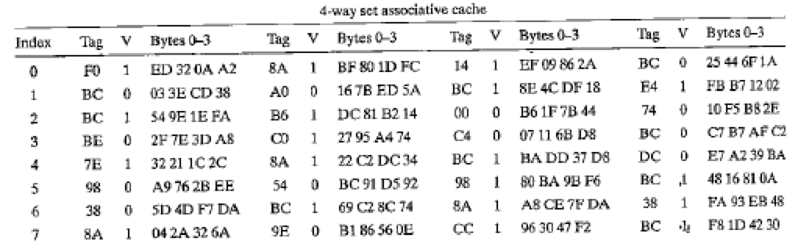

- The cache is 4-way set associative (E = 4), with a 4-byte block size (B = 4) and eight sets (S= 8).

Consider the following cache state. All addresses, tags, and values are given in hexadecimal format. The Index column contains the set index for each set of four lines. The Tag columns contain the tag value for each line. The V columns contain the valid bit for each line. The Bytes 0-3 columns contain the data for each line, numbered left to right starting with byte 0 on the left.

- A. What is the size (C) of this cache in bytes?

- B. The box that follows shows the formal of an address(1 bit per box). Indicate (by labeling the diagram) the fields that would be used to-determine the following:

CO. The cache block offset

CI. The cache set index

CL. The cache tag

Learn your wayIncludes step-by-step video

Chapter 6 Solutions

Computer Systems: Program... -Access

Additional Engineering Textbook Solutions

Starting Out with Java: From Control Structures through Data Structures (4th Edition) (What's New in Computer Science)

C Programming Language

Starting Out With Visual Basic (7th Edition)

Introduction to Programming Using Visual Basic (10th Edition)

Introduction To Programming Using Visual Basic (11th Edition)

Starting Out with Java: From Control Structures through Objects (7th Edition) (What's New in Computer Science)

- Let's pretend for a moment that we have a byte-addressable computer with fully associative mapping, 16-bit main memory addresses, and 32 blocks of cache memory. The following holds true if each block is 16 bits in size:a) Determine how many bytes the offset field is.Measure the tag field's width and height in pixels (b).arrow_forwardQ. Consider a system with 4-way set associative cache of 256 KB. The cache line size is 8 words (32 bits per word). The smallest addressable unit is a byte, and memory addresses are 64 bits long. (a) How many bits are used for TAG and INDEX fields of cache mapping?arrow_forwardConsider a main memory with size 128 Mbytes with cache size 64 Kbytes and memory block is 4 bytes. Determine how to split the address (s-r, r, w) for direct mapping. Determine how to split the address (s, w) for associative mapping. Determine how to split the address (s-d, d, w) for set associative mapping. Assume each cache set is 2 lines of cache.arrow_forward

- Suppose we have a byte-addressable computer using direct mapping with 16-bit main memory addresses and 32 blocks of cache. If each block contains 8 bytes. a. Determine the number of bits of the tag field. b. To which cache block would the hexadecimal address 0x2468 map? c. What is the tag of the hexadecimal address 0x2468arrow_forwardConsider a direct-mapped cache memory with 12-bit addresses. The cache is byte-addressable. We have B = 16 bytes per block and S = 8 sets. For the address shown below. Indicate which bits correspond to the cache set index, tag bits, and block offset. Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0arrow_forwardConsider a word-based, four-way set associative cache with 64 bits. Each line has eight words, and the total number of sets is forty-nine thousand. What is the cache's size? a) 1 megabyte b) 10 megabytes c) 4 megabytes d) 512 kilobytesBefore a network can be called effective and efficient, three requirements must be met. Please write a short description in your own words of the one you've chosen.arrow_forward

- For a direct-mapped cache design with a 32-bit address, the following bits of the address areused to access the cache.Tag Index Offset31–10 9–6 5–0a– What is the cache block size (in words)? b – How many entries does the cache have? c – What is the ratio between total bits required for such a cache implementation overthe data storage bits?arrow_forwardSuppose a byte-addressable computer using set associative cache has 8M byes of main memory and a cache of 128 blocks, where each cache block contains 64 bytes. a) If this cache is 4-way set associative, what is the format of a memory address as seen by the cache, that is, what are the sizes of the tag, set, and offset fields? b) If this cache is 16-way set associative, what is the format of a memory address as seen by the cachearrow_forwardSuppose we have a byte-addressable computer with a cache that holds 8 blocks of 16 bytes each. Assuming that each memory address has 16 bits, to which cache block would the hexadecimal address 0x13F map if the computer uses direct mapping? Blocks are numbered starting at 0.arrow_forward

- Consider a small 2-way set associative cache memory, consisting of 4 blocks. For choosing the block to be replaced, use LRU scheme. Consider that block address 4 and 2 are already there in cache. The number of cache misses for the following sequence of block addresses 4, 6, 8, 16, 2, 2, 4 are?arrow_forwardSuppose a byte-addressable computer using set associative cache has 2^24 bytes of main memory and a cache size of 64K bytes, and each cache block contains 32 bytes. a) If this cache is 2-way set associative, what is the format of a memory address as seen by the cache, that is, what are the sizes of the tag, set, and offset fields? b) If this cache is 4-way set associative, what is the format of a memory address as seen by the cache?arrow_forwardConsider a main memory with size 512MB with cache size 64KB and memory block is 4 bytes. Assume that the memory word is 1 byte . Answer following question How many address bits are required ti address the main memory locations ? How many blocks are there in the cache memory? Determine how to split the address (s-r, d ,w )for direct mapping? Determine how to split the address (s-d, d ,w )for set associative mapping .Assume each cache set is 4 line of cachearrow_forward

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON

Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON

Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON

C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning

Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education