Computer Systems: Program... -Access

3rd Edition

ISBN: 9780134071923

Author: Bryant

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Textbook Question

Chapter 6, Problem 6.40HW

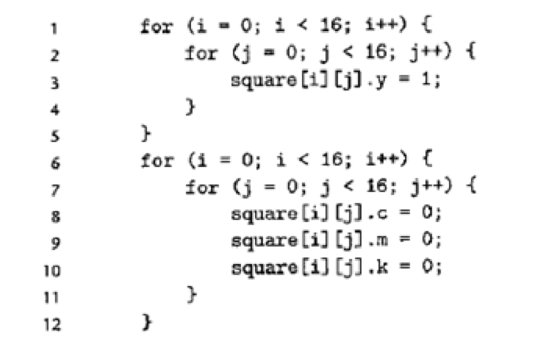

Given the assumptions in Problem 6.38, determine the cache performance of the following code:

- A. What is the total number of writes?

- B. What is the total number of writes that miss in the cache?

- C. C What is the miss rate?

Expert Solution & Answer

Want to see the full answer?

Check out a sample textbook solution

Students have asked these similar questions

Is there a way to find out which parts of a log entry a certain log processing function can read? The following code determines the typical number of cache misses per entry while using 64-byte cache blocks and no prefetching.

Determine the cache performance of the following code:1 for (i = 0; i < 16; i++){2 for (j = 0; j < 16; j++) {3 total_x += grid[j][i].x;4 total_y += grid[j][i].y;5 }6 }A. What is the total number of reads?B. What is the total number of reads that miss in thecache?C. What is the miss rate?D. What would the miss rate be if the cache were twice asbig?

This chapter explains how to implement the four cache replacement policies.

Chapter 6 Solutions

Computer Systems: Program... -Access

Ch. 6.1 - Prob. 6.1PPCh. 6.1 - Prob. 6.2PPCh. 6.1 - Prob. 6.3PPCh. 6.1 - Prob. 6.4PPCh. 6.1 - Prob. 6.5PPCh. 6.1 - Prob. 6.6PPCh. 6.2 - Prob. 6.7PPCh. 6.2 - Prob. 6.8PPCh. 6.4 - Prob. 6.9PPCh. 6.4 - Prob. 6.10PP

Ch. 6.4 - Prob. 6.11PPCh. 6.4 - Prob. 6.12PPCh. 6.4 - Prob. 6.13PPCh. 6.4 - Prob. 6.14PPCh. 6.4 - Prob. 6.15PPCh. 6.4 - Prob. 6.16PPCh. 6.5 - Prob. 6.17PPCh. 6.5 - Prob. 6.18PPCh. 6.5 - Prob. 6.19PPCh. 6.5 - Prob. 6.20PPCh. 6.6 - Prob. 6.21PPCh. 6 - Prob. 6.22HWCh. 6 - Prob. 6.23HWCh. 6 - Suppose that a 2 MB file consisting of 512-byte...Ch. 6 - The following table gives the parameters for a...Ch. 6 - The following table gives the parameters for a...Ch. 6 - Prob. 6.27HWCh. 6 - This problem concerns the cache in Practice...Ch. 6 - Suppose we have a system with the following...Ch. 6 - Suppose we have a system with following...Ch. 6 - Suppose that a program using the cache in Problem...Ch. 6 - Repeat Problem 6.31 for memory address0x16E8 A....Ch. 6 - Prob. 6.33HWCh. 6 - Prob. 6.34HWCh. 6 - Prob. 6.35HWCh. 6 - Prob. 6.36HWCh. 6 - Prob. 6.37HWCh. 6 - Prob. 6.38HWCh. 6 - Prob. 6.39HWCh. 6 - Given the assumptions in Problem 6.38, determine...Ch. 6 - You are writing a new 3D game that you hope will...Ch. 6 - Prob. 6.42HWCh. 6 - Prob. 6.43HWCh. 6 - Prob. 6.45HWCh. 6 - Prob. 6.46HW

Additional Engineering Textbook Solutions

Find more solutions based on key concepts

Suppose you have a chess program that can evaluate 10 million nodes per second. Decide on a compact representat...

Artificial Intelligence: A Modern Approach

What is a variable that is used to accumulate a total called?

Starting out with Visual C# (4th Edition)

3.12 (Date Create a class called Date that includes three pieces Of information as data

members—a month (type ...

C++ How to Program (10th Edition)

Can you reference an instance variable by name within the definition of a non-static method without using a cla...

Java: An Introduction to Problem Solving and Programming (7th Edition)

A pet store sells dogs, cats, birds, and hamsters. Write a declaration for an enumerated data type that can rep...

Starting Out with Java: Early Objects (6th Edition)

Write a function void switchEnds(int array, int size); that is passed the address of the beginning of an array ...

Starting Out with C++: Early Objects

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Similar questions

- What does write back mean in terms of cache? Group of answer choices a. When an error occurs in memory, the cache is written back to the memory. b. When a bit in the cache is changed, the entire block is written to memory. c. When a line is evicted, the block it contains is written to memory.arrow_forwardFor a direct-mapped cache design with a 32-bit address, the following bitsof the address are used to access the cache. Use the table below. a. What is the cache block size (in words)?b. How many entries does the cache have?c. What is the ration between total bits required for such a cache implementation overthe data storage bit?arrow_forwardFor a direct-mapped cache design with a 32-bit address, the following bits of the address are used to access the cache.Tag Index Offset31–10 9–5 4–01. What is the cache block size (in words)?2. How many entries does the cache have?3. What is the ratio between total bits required for such a cache implementation over the data storage bits?Starting from power on, the following byte-addressed cache references are recorded. Address 0 4 16 132 232 160 1024 30 140 3100 180 2180 How many blocks are replaced? What is the hit ratio? List the fi nal state of the cache, with each valid entry represented as a record of <index, tag, data>arrow_forward

- In the event of an unsatisfied cache request, what should happen to the block being sent to the main memory from the write buffer?arrow_forwardFor a direct-mapped cache design with a 32-bit address, the following bits of the address areused to access the cache.Tag Index Offset31–10 9–6 5–0a– What is the cache block size (in words)? b – How many entries does the cache have? c – What is the ratio between total bits required for such a cache implementation overthe data storage bits?arrow_forwardSuppose that in 1000 memory references there are 50 misses in the first-level cache, 20 misses in the second-level cache, and 5 misses in the third-level cache. Assume the miss penalty from the L3 cache to memory is 100 clock cycle, the hit time of the L3 cache is 10 clocks, the hit time of the L2 cache is 4 clocks, the hit time of L1 is 1 clock cycle. What is the average memory access time?arrow_forward

- In what ways would it be difficult to design a cache replacement method that works with every given address sequence?arrow_forwardImagine the difference that exists between a cache that is completely associative and one that is directly mapped.arrow_forwardWhat Is the Definition of Cache Performance?arrow_forward

- QUESTION 22 Assume a cache has 16 entries. How many index bits are needed to address the cache? a. 2 b. 4 c. 5 d. 16 QUESTION 23 Which of the following statements about cache write policy is NOT true? a. A dirty bit is used to implement a write back approach. b. A cache entry with dirty bit = 1 means the data inside is safe to be replaced. c. A write back approach is not suitable for multiple processors accessing the same memory. d. A write back approach is typically faster than a write through approach. QUESTION 25 Which of the following statements is true of normalized scientific notation? a. 3.06 x 10^3 is in decimal normalized scientific notation b. 0.30 x 10^3 is in decimal normalized scientific notation c. 0.11 x 10^5 is in binary normalized scientific notation d. 10.01 x 10^5 is in binary normalized scientific notationarrow_forwardHow does the cache know whether it contains a copy of the word at address A?arrow_forwardTo what extent does the specified log processing function have access to each field of a log entry? The following code determines the typical number of cache misses per entry while using 64-byte cache blocks and no prefetching.arrow_forward

arrow_back_ios

SEE MORE QUESTIONS

arrow_forward_ios

Recommended textbooks for you

Systems ArchitectureComputer ScienceISBN:9781305080195Author:Stephen D. BurdPublisher:Cengage Learning

Systems ArchitectureComputer ScienceISBN:9781305080195Author:Stephen D. BurdPublisher:Cengage Learning

Systems Architecture

Computer Science

ISBN:9781305080195

Author:Stephen D. Burd

Publisher:Cengage Learning

Instruction Format (With reference to address); Author: ChiragBhalodia;https://www.youtube.com/watch?v=lNdy8HREvgo;License: Standard YouTube License, CC-BY