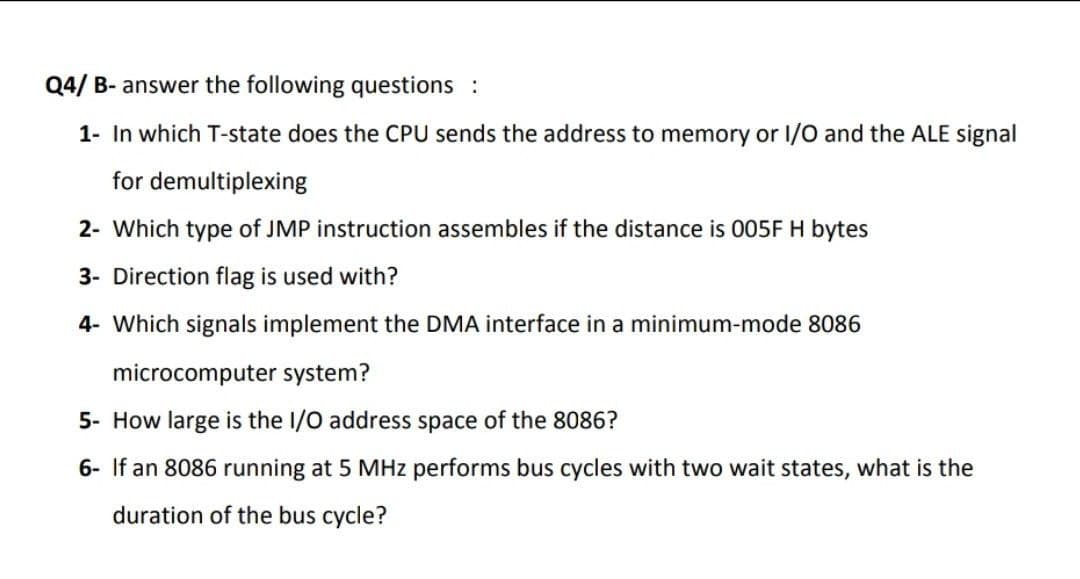

Q4/ B- answer the following questions : 1- In which T-state does the CPU sends the address to memory or I/0 and the ALE signal for demultiplexing 2- Which type of JMP instruction assembles if the distance is 005F H bytes 3- Direction flag is used with?

Q: Assume that the physical address of the instruction is (D6A92H) and the code 2 Bandwidth segment…

A: Memory addressing schemes:1. An Absolute Address, such as 04A26H, is a 20 bit value that directly…

Q: What happens if an instruction is not accepted and it writes to VA page 30? In the following…

A: Introduction: When a command is sent to VA page 30: If the instructions want to write to Virtual…

Q: Pipelining in 8086 processors is achieved using which of the following option: O a. By using the…

A: Here have to determine correct option for 8086 pipeline.

Q: Determine the specific type of addressing mode (SMALL LETTERS only) and compute for the address/es.…

A: Determine the specific type of addressing mode (SMALL LETTERS only) and compute for the address/es.…

Q: b) Given the following register and memory values, what values do the following ARM instructions…

A: Value of R0 register is given below after each given ARM instructions

Q: If this Datapath is currently executing the instruction, LW $s1, -4($t1), register s1 contains the…

A: It is defined as the Operator at the heart of the control room with its latest fully integrated…

Q: 4. Which is the speedup that can be obtained on 100 processors if 93% of the program is ideally…

A: This can be achieved using Amdahl's law. This law states that the maximum speedup that is possible…

Q: 22: The content of the top of a memory stack is 5420. The content of the stack pointer SP is 1789. A…

A: Answer : I attached an answer please have a look once.

Q: If the first instruction "LXI H, 1100H" is positioned at address 7000H in memory, at what address…

A:

Q: Q1) if you know the SS-1245H ,DS-5678H, BP- 3ACDH ,BX-23ADH, SI-9ABDH,Select the true value for…

A: ANSWER: 64F3EH Explanation: The memory address register is utilized to deal with the address moved…

Q: The jump instruction (j) allows the execution to start from a new address. Opcode (6 bits) Address…

A: Question from jump instruction. jump(X) means we will jump to Address' X' and start execution from…

Q: Given the following branch instruction and location, answer the following questions about it.…

A: Given that: 0X10000 , 0Xb5000184At present, the PC is at 0X10000 * Type of branch Instruction:…

Q: 2. What will be the state at the top of the stack after the following sequence of operations…

A: The question is to find state at the top of the stack after the given sequence of operations.

Q: rgy consumed by the worst-case MIPS instruction, and how m

A: Below the energy consumed by the worst-case MIPS instruction

Q: Q1: what is the addressing mode for the following instructions: 1. SUB A,B,C 2. OR A,B 3. ADD R1 4.…

A: Instructions Addressing Mode Explanation 1. SUB A,B,C Implied addressing mode The SUB is a…

Q: corresponding Which one of the following is the binary representation of the machine code that to…

A: Given that, opcode of lw = 35 register is $t1=9 register $t2= 10 lw $t1, 20($t2)

Q: A - Mention how do the following instructions differ 1- NEG & NOT 2- DIV & IDIV 3- AND & TEST 4- CMP…

A: A microprocessor is a computer processor that incorporates the functions of a central…

Q: Determine the specific type of addressing mode (SMALL LETTERS only) and compute for the address/es.…

A: the given instruction is MOV EIP, [BP+BAFDH] ; ( It is not a valid instruction, because EIP can not…

Q: 8.3 An Acc-ISA CPU executes the following instructions using 3-bit op-codes and 5-bit address or 2's…

A: Here is the answer:-

Q: Q4) Suppose that DS-1020H, SS-2010H, BX-0300H, BP-1010H, and DI= 1100H. Determine the memory address…

A: Given that, DS=1020H SS=2010H BX=0300H BP=1010H and DI=1100H Given Instructions are:MOV [DI+300], AL…

Q: 2. Write an instruction sequence that will initialize the ES register with the immediate value…

A: Q)Write instruction sequences that will initialize the ES register with the immediate value 1020H.…

Q: How is the stack top address calculated? [3] Identify the addressing modes, the source, and the…

A: Note: As, per company guidelines we are supposed to answer only one question at a time. so, we have…

Q: Consider the diagram below that shows the fetching data flow for an indirect cycle along with the…

A: What will be the content of the MAR register after finishing the execution of the indirect cycle for…

Q: is the effective address that is targeted by the store instruction whose code word in binary is:…

A: It is defined as programs can be asked from control statements, array, string, oops etc. Java basic…

Q: If R1 = 0xEF00DE12, R2 = 0x0456123F, R5 = 4, R6 = 28; Find the values of the destination registers…

A: Shifters :- 1.Logical Shift Left(LSL):- In 32 bit register, it shift left for specified number of…

Q: The branch instruction allows the execution to go backward or forward starting from a new a Opcode…

A: answer is option f f.1000. the branch instruction should be 1000

Q: PLACE .FILL X45A7 LDI R3, PLACE The assembler puts the translated version of the LDI instruction…

A: Consider the instructions,PLACE .FILL x45A7LDI R3, PLACE• Here, the LDI instruction follows into the…

Q: Explain how the 8086 microprocessor will code the following instruction into successive memory…

A: Solution ::

Q: 2- Find the physical destination address of last instruction below MOV BX,0AAH MOV AX,1BBH MOV DS,AX…

A: Please give positive ratings for my efforts. Thanks. ANSWER BX = 0AA H AX = 1BB H DS = AX = 1BB…

Q: Q1:Suppose the initial physical address of a segment register is given by 0E41:A02EH. Determine the…

A: The solution for the above given question is given below:

Q: n ? a- 1ACF3H b- 1A32H c- 1AC93H d- 1ACFH

A: The code segment has a value of 1ACFH with 0003H in the instruction pointer what physical address…

Q: QI) I BX=1000, DS-0200, SS=0100, CS-0300 and AL=EDH, for the following instruction: MOV [BX] +…

A: Here is Solution for Above Problem :: Q1). Given Data : BX = 1000 DS = 0200 SS = 0100 CS = 0300 AL…

Q: (a) In the given 8086 block diagram, write down the sizes of the (i) registers (ii) segments (iii)…

A: The answer is given below:-

Q: b. Following packed SIMD data type of X86 architecture interpret packed single precision and packed…

A: Solution a :- Two address instructions will contain only two operand addresses in the instruction.…

Q: Given the following memory addresses and opcodes to be executed, if the current value of the…

A: Please upvote/like .I am providing you the correct answer below. Please. What is…

Q: Compute the binary representation of the following mips instruction: lw $t4, 5($s4)

A: opcode => lw => 100011 base => $s4 => 10100 rt => $t4 => 01100…

Q: Assume that the Intel 8086 registers AL, BL, CL, and DL have the following values Gn Hexadecimal)…

A: Question 1) XCHG BL, DL will exchange the values of BL with DL , thus BL= AB DL = CD. Question 2)…

Q: The jump instruction () allows the exécution to start from a new address. Opcode (6 bits) Address…

A: Question from jump instruction. jump(X) means we will jump to Address' X' and start execution from…

Q: 1. Assume the program counter has value 0XFAFAFAFA and you run the MIPS instruction "beq $t1, $t2…

A: Dear Student, 1) beq Instruction in MIPS increment the PC by the address passed in beq also an extra…

Q: Determine the specific type of addressing mode (SMALL LETTERS only) and compute for the address/es.…

A: We have given an Instruction , we have to find the effective address , physical address , etc. Out…

Q: B- Write a single instruction that loads AX from address 0200 H and DS from address 0202H.

A:

Q: is the effective address that is targeted by the store instruction whose code word in binary is:…

A: It is defined as the effective address of an operand is represented in the instruction. Some…

Q: In the JMP instruction, how many bits are there for determining the target address? Select one: O a.…

A: SummaryAnswer: C (22bits) There are numerous different forms of jumps relative, tentative,…

Q: NA. F

A: An assembly language is a programming language that usually has one instruction for the processor to…

Q: List three possible logical addresses corresponding to physical address 143F?

A: The, given question regarding logical address and physical address.

Q: 4) Two actions must be completed before a CBZ's branch can be taken, actions that take time.…

A: assume if CBZ instruction is at address 40 and the CBZ's third operand is 32 then the target address…

Q: What is the main difference between the JMP instruction and the JSRR instruction? O There is no…

A: JMP is used to perform the unconditional jump - to the address specified operand. as an example, JMP…

Q: Determine the specific type of addressing mode (SMALL LETTERS only) and compute for the address/es.…

A: the given instruction is MOV EIP, [BP+BAFDH] ; ( It is not a valid instruction, because EIP can…

Q: Determine the specific type of addressing mode (SMALL LETTERS only) and compute for the address/es.…

A: the given instruction is MOV EIP, [BP+BAFDH] ; ( It is not a valid instruction, because EIP can not…

Q: During the processing of which of the following instructions is the use of an adder not required?…

A: In step 2, you will get the answer.

Step by step

Solved in 2 steps

- If a microprocessor has a cycle time of 0.5 nanoseconds, what’s the processor clock rate? If the fetch cycle is 40% of the processor cycle time, what memory access speed is required to implement load operations with zero wait states and load operations with two wait states?What is the name of the Intel technology that allows a processor to handle two threads at the same time?How does pipelining improve CPU efficiency? What’s the potential effect on pipelining’s efficiency when executing a conditional BRANCH instruction? What techniques can be used to make pipelining more efficient when executing conditional BRANCH instructions?

- The MSP430 can move/copy a byte or a word at a time using the instructions mov.b and mov.w respectively. In particular, the instructions mov.b &source_address, R4 mov.w &source_address, R4 copy the byte or word that resides at the given address (&source_address) to the given destination (the core register R4 in the CPU). Which of the following instructions are valid? (a) mov.b &0x1C03, R4 (b) mov.w &0x1C02, R4 (c) mov.b &0x1C00, R4 (d) mov.w &0x1C05, R4QUESTION 2 Discuss with examples the main difference between system programming and application programming and explain in your own words how each of these can be carried out in the computer system. With your knowledge in memory addressing modes and using the given opcodes LDA = 00 0000 0000 (00) 0 (x) What will be the content of the address loaded into the accumulator? b. With your knowledge in memory addressing mods and using the given opcodes STCH = OX54 Buffer = 1000 0101 0100 (00) 1 (x) 000 1000 0000 0000 () 011 0000 0000 0000 () What will be target address? Briefly explain the usage of the JSUB and RSUB instruction sets in an SIC architecture codingWhich memory address in Interrupt Vector Table (IVT) stores the higher byte of the segment part forthe beginning address of ISR that corresponds to ITC 15 H? Justify your answer with calculation. give diagram if needed

- 10. Q1 : What is an atomic instruction? Show that if the wait operation is not executed atomically, then mutual exclusion may be violated Q2: What is spinlock? Discuss the advantage and disadvantage of using spinlock. Why do you think Solaris, Linux, and Windows 2000 use spinlocks as a synchronization mechanism only on multiprocessor systems and not on single- processor systems?Please answer both questions a)There are 3 forms of Program Memory Addressing Modes: Direct, Relative and Indirect. Explain/Illustrate what happens to CS and IP registers if the JMP THERE instruction is stored at memory address 10000H (CS=1000H, IP=0000H) and the address of THERE is:(i) 10020H(ii) 30000H(b) Determine whether the JMP THERE instructions are SHORT, NEAR or FAR jump. Explain your answer.Q:Answer the following sentence with (True) or (False) and correct the false answer: 1. You can input data of size 16-bit through the fixed port. 2. In the maximum mode, the status signals S₁, S₂ and S3 are controlled by the bus controller. 3. HLDA is an output signal. 4. In 8086, when executing the instruction MOV AL, [SI+100D H] where SI-100AH, Ao=0 and BHE=1 5. When S, is 0, the TF is disabled.

- 33. Which one of the following is true with regard to a CPU having a single interrupt request line and single interrupt grant line…??i) Neither vectored nor multiple interrupting devices is possible.ii) Vectored interrupts is not possible but multiple interrupting devices is possible.iii) Vectored interrupts is possible and multiple interrupting devices is not possible.iv) Both vectored and multiple interrupting devices is possible. a. iii b. i,iv c. ii,iii d. iii,iv4. Memory and Addressing Modes The state of the CPU and memory is represeated by this diagram. _m Address | Value X [ | =] | S R [pc_[srooo | s Jsoueo] [Fag(p) [N [v[1]e o i [2]c] [vaive Jofo]1]ofofo]1]1] a) Value of A after execution of LDA #50D? b) Value of A after execution of LDA #S0F? €) Value of Y after execution of LDY $0D? ) Value of Y after LDY ${000F), X? ) Value of Y after LDY ($0F), X2 please show workings!1. Name all of the general purpose registers and some of their special functions. 2. How are the segment registers used to form a 20-bit address? 3. (a) If CS contains 03E0H and IP contains 1F20H, from what address is the next instruction fetched? (b) If SS contains 0400H and SP contains 3FFEH, where is the top of the stack located? (c) If a data segment deigns at address 24000H, what is the address of the last location in the segment? 4. Explain what the instruction array and data caches are used for. 5. What is the EU and BIU, and what purpose in the microcomputer? 6. Two memory locations, beginning at address 3000H, contain the bytes 34H and 12H. What is the word stored at location 3000H? See Figure 2.26 for details. Address 3000 Data 34 3001 12 Figure 2.26 For question 6 7. What is a physical address? What are the differences between the 8086 logical and physical memory maps? 8. May memory segments overlap? If so, what is the minimum number of overlapped bytes…