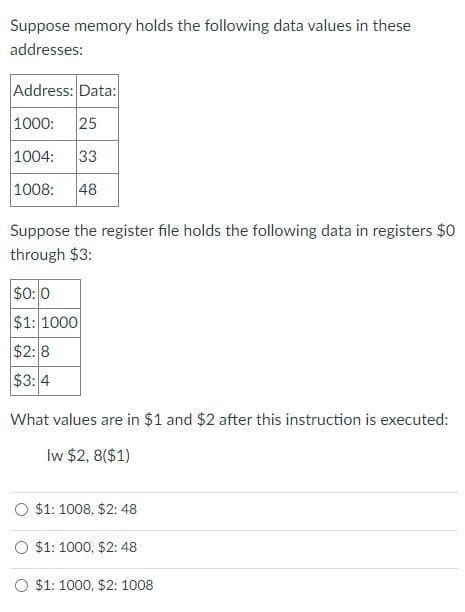

Suppose memory holds the following data values in these addresses: Address: Data: 1000: 25 1004: 33 1008: 48 Suppose the register file holds the following data in registers $ through $3: $0: 0 $1: 1000 $2:8 $3:4 What values are in $1 and $2 after this instruction is executed Iw $2, 8($1) O $1: 1008, $2: 48 $1: 1000, $2: 48 $1: 1000, $2: 1008

Q: Address Content 50 10 51 57 52 53 21 OA 54 55 52 01 56 32 57 СО 58 59 00 Suppose the memory cells at…

A: Answer: I have given answer in the brief examples

Q: 2) A computer uses a memory unit of 1048576K word made of 50 bit each. A binary instruction code is…

A: Note: Answering the first three subparts i.e. a,b, and c. Given Data : Size of memory word(s) =…

Q: 1. Suppose the Vole memory cells from addresses 0x00 to 0x05 contain the bit patterns given in the…

A: According to the Bartelby guideline we are suppose to answer only one question at a time. Kindly…

Q: For this assignment, you are to write a MIPS assembly language program using the MARS IDE and assume…

A: Answer :

Q: Consider the basic computer whose microinstruction set is described by table 1. If the f Address E02…

A: It is defined as a type of computer memory used to quickly accept, store, and transfer data and…

Q: A process occupies a computer's main memory locations starting at address 76524. What is the logical…

A: Defined the given statement

Q: [5] The following table represents a small memory with 4 locations: Address Data 0001 1110 0100 0011…

A: Answer:)

Q: Consider an operating system that uses Segmentation. Given an address [S,D], where S is the segment…

A: given an operating system that uses Segmentation. Given an address [S,D], where S is the segment and…

Q: Given the following memory values and a one-address machine with an accumulator, what values do the…

A: Actually, the operand which is stored n particular memory location is called as addressing mode.

Q: The jump instruction (j) allows the execution to start from a new address. Opcode (6 bits) Address…

A: Question from jump instruction. jump(X) means we will jump to Address' X' and start execution from…

Q: Suppose the Vole memory cells at addresses 0XB0 to 0XB8 contain the bit patterns given in the…

A: The solution for the above given question is given below:

Q: Use the register and memory values in the tables below for the next questions. Assume a 32-bit…

A: a) add $t3, $t2, $t1 implies adding the contents of register t1 to the contents of register t2 and…

Q: Q4/ A- How many: 1- memory locations can be addressed by a microprocessor with 14 address lines? 2-…

A: Question 4 from Memory management system. In this, we are asked how many address lines required for…

Q: 1. A segment is an area of memory that includes up to bytes. 2. How large is a segment in the 8086?…

A: Hi there, Please find your solution below, I hope you would find my solution useful and helpful.…

Q: Assume a CPU has 8 registers (3 bits), 32 op-codes (5 bits), 15-bit addresses, 16- bit integers.…

A: An instruction format defines the different component of an instruction. The main components of an…

Q: 1- Memory locations can be addressed by a microprocessor with 14 address lines? 2- Chips are…

A: 8086 System 8086 Microprocessor is an advanced version of the before version of 8086 which is teh…

Q: Let us consider a memory that includes two instructions. First instruction is located at memory…

A: The solution for the above given question is given below:

Q: A simple processor shown in the figure, having the following basic calculation ability: Addition…

A: On a computer, a memory address (MAR) register is a CPU that stores the address where the data will…

Q: the starting address of the RAM is 00000H. RAM1 = 64K , RAM2 = 64K , RAM3 = 32K , RAM4 = 64K ,and…

A: The starting addresses of all memory chips are integer multiple of the sizes of the corresponding…

Q: A digital computer has a memory unit with 24 bits per word. The instruction set consists of 150…

A: Introduction: An instruction format defines the different component of an instruction. The main…

Q: Consider an equation, W = (X + Y ) * Z is run using CISC one address format and illustration of its…

A: We need to find the result and storage location of result for the given code.

Q: Let us consider a memory that includes two instructions. First instruction is located at memory…

A: Given

Q: A certain computer has a memory of 1M words, and each word is 32 bits long. Each instruction is 32…

A:

Q: Answer the following questions pertaining to the example program given. After the program is…

A: After the program is executed, list the values contained in each of the registers, and memory…

Q: n ? a- 1ACF3H b- 1A32H c- 1AC93H d- 1ACFH

A: The code segment has a value of 1ACFH with 0003H in the instruction pointer what physical address…

Q: Consider the following registers X and Y of a certain computer contains the decimal values 1024 and…

A: Introduction. Given, register X=1024 register Y=4096 Three instructions, are given:- I1.…

Q: Let us consider a memory that includes two instructions. First instruction is located at memory…

A: CLICK HERE TO GET MORE FREE SOLUTIONS :: Solution :: // C program for the above approach…

Q: 1. The hypothetical machine of figure 3.4 also has two I/O instructions: 0011= Load AC fro I/O 0111=…

A: Given:

Q: Let us consider a memory that includes two instructions. First instruction is located at memors…

A: It can be approached as: The instruction consists of opcode and operands. Given the instruction…

Q: Question 35 A processor running a program makes 100 accesses to memory addresses. 80% are to L1…

A: A processor running a program makes 100 accesses to memory addresses.80% are to L1 only,10% are to…

Q: Assume a CPU with a fixed 32-bit instruction length has the following instruction forma

A: a. Op code + mode = 7 + 5 = 12 bits, leaving 22 bits for the operands. With 3 registers,each uses 9…

Q: A computer with a 32-bit word uses an instruction format that includes direct and indirect…

A: The answer given as below:·

Q: Suppose the hypothetical processor has two I/O instructions: 0011=Load AC from I/O 0111=Store AC to…

A: Given:- 0011=Load AC from I/O0111=Store AC to I/O

Q: Assume a CPU has 8 registers (3 bits), 32 op-codes (5 bits), 15-bit addresses, 16- bit integers.…

A: CPU has 8 registers (3 bits), 32 op-codes (5 bits), 15-bit addresses, 16-bit integers. Which ISA…

Q: 2. Given the following series of instructions (left two columns). After each instruction has been…

A: In computer engineering, computer architecture is a set of rules and methods that describe the…

Q: Assume a CPU has 8 registers (3 bits), 32 op-codes (5 bits), 15-bit addresses, 16-bit integers.…

A: ISA: ISA is the part of the processor that is noticeable to the programmer or compiler author. The…

Q: A computer has a 256K word addressable memory Module with 16 bits per word. The instruction set…

A: Pipelining can be described as the procedure of accumulating instructions from the processor in the…

Q: Problem Given the following memory values and a one-address machine with an accumulator, what…

A: a) Immediate addressing mode loads the constant value 20 as an operand to accumulate. AC=20

Q: 1. Assume the program counter has value 0XFAFAFAFA and you run the MIPS instruction "beq $t1, $t2…

A: Dear Student, 1) beq Instruction in MIPS increment the PC by the address passed in beq also an extra…

Q: Q.1. A computer uses a memory unit with 1024 K words of 32 bits each (as shown in the figure…

A: 1024 K = 210 × 210 = 220 64= 26 Address: 20 bits Register code: 6 bits Indirect…

Q: ISA of a hypothetical CPU 1 Address Memory: Address Data – (8-bits) LOAD M 100 25 STORE M 101 90 ADD…

A: Note: According to guidelines we are supposed to answer only first 3-sub part at a time. please…

Q: The code segment has a value of 0ACFH with 0123H in the instruction pointer what physical address…

A: b)04E13H

Q: Consider a 1-address CPU that has a memory unit with 128K words of 32 bits each. An instruction is…

A: Size of 1 word = 32 bits Size of instruction = 1 word = 32 bits Addressing mode = 2 bits Register…

Q: Consider a word-addressable computer with 32 bits per word. The instruction set consists of 30…

A: Answer : given data, word addressable computer instruction size = 32 bits possible instruction…

Q: Question 11 The decoding of 80x86 instructions are simpler than instructions in ARM processors. O…

A: Here, we have to provide True/False for the above questions.

Q: computer is available without an instruction pointer (IP) or program counter (PC). Instead, all…

A: ANSWER : A) MEMORY WORD CONSISTS 256K, PRE EACH WORD CONSISTS 32 BIT ACOORDING TO BASIC OF OUR…

Q: Suppose a byte-addressable computer using 4-way setassociative cache has 216 words of main memory…

A: Due to the byte memory, this meant 1 Phrase = 1 byte. The main size of the memory therefore = 216…

Q: .in a code space of 8Kbytes mapping from address 0X1000. What is the last address available to store…

A: Over here given a code section of 8k bytes. Means total size is 8192.

Q: Given the following snippet of byte addressable memory with the base address already loaded in…

A: Holds both instructions and data With k address bits and n bits per locationn is typically 8 (byte),…

Trending now

This is a popular solution!

Step by step

Solved in 2 steps

- _____ is a CPU design technique in which instruction execution is divided into multiple stages and different instructions can execute in different stages simultaneously.Most Intel CPUs use the __________, in which each memory address is represented by two integers.A(n) ________________ instruction always alters the instruction execution sequence. A(n) ______________ instruction alters the instruction execution sequence only if a specified Condition is true.

- How does pipelining improve CPU efficiency? What’s the potential effect on pipelining’s efficiency when executing a conditional BRANCH instruction? What techniques can be used to make pipelining more efficient when executing conditional BRANCH instructions?Assume a CPU with a fixed 32-bit instruction length has the following instruction format:opcode mode [operand1] [operand2] [operand3]The mode encodes the number of operands and each operand’s mode. For instance, one mode indicates three registers, another indicates two registers and an immediate datum, another indicates a main memory reference, etc. Assume there are 94 instructions and 22 modes. Answer the following.a. One mode indicates three registers. How many registers can be referenced in this mode?b. One mode indicates two registers and an immediate datum in two’s complement. Assuming there are 32 registers, what is the largest immediate datum that can be referenced?c. One mode has a destination register and a source memory address (an unsignednumber). Assuming 16 registers, what is the largest memory reference available?d. One mode has two memory addresses, both using base displacement. In both, the basesare stored in index registers and the displacements are specified in the…Consider a Computer which has a memory which is capable of storing 4096 K words and each word in memory can be of size 32 bits. The computer supports a total of 6 addressingmodes, and it has 60 computer registers. The computer supports instructions, where each instruction consists of following fields: Mode Operation code Register Register Memory AddressGiven that each instruction will be stored in one memory word, discuss with a suitable diagram the format of instruction by specifying number of bits for each field of instruction. Discuss each field of instruction.

- 1. T/F - if (B)=006000 (PC)=003600 (X)=000090, for the machine instruction 0x032026, the target address is 003000.2. T/F – PC register stores the return address for subroutine jump.3. T/F – S register contains a variety of information such as condition code.4. T/F – INPUT WORD 1034 – This means Operating system should reserve 1034 bytes in memory5. T/F - In a two pass assembler, adding literals to literal table and address resolution of local symbol are done using first pass and second pass respectively.Suppose that each of the 4 processors in a shared memory multi-processor system is rated at 400 MIPS. A program contains a purely sequential part that accounts for 22% of the program’s execution time on a single processor. The remaining code can be partitioned into three independent parts (A, B, and C). Running on a single processor, part A accounts for 30% of the program’s execution time, part B accounts for 18%, and part C accounts for 30%. What is the apparent MIPS rating for the program if it is run on the 4-processor system and the sequential part must be completed before any of the remaining independent parts (A, B or C) can run in parallel?hi can u anwser this qustion plesc ? Consider a Computer which has a memory which is capable of storing 4096 K words and each word in memory can be of size 32 bits. The computer supports a total of “K” addressing modes, and it has “M” computer registers. The computer supports instructions, where each instruction consists of following fields: Mode Operation code Register Register Memory AddressGiven that each instruction will be stored in one memory word, discuss with a suitable diagram the format of instruction by specifying number of bits for each field of instruction. Discuss each field of instruction.Note: Choose your own values for K (number of addressing modes) and M (number of Registers) k=8 m=50

- Convert the given code fragment to assembly code fragment, using only instructions of the following types. These instructions are generally discussed in class. Here X,Y,Z are any memory locations; R, R1, R2 are any general registers; L is a label in the code (you can use any names as labels, ex. L, L1, L2 etc. ). load X, R //copy contents of memory location X into R. store R, X //Store contents of R into Mem location X cmp R1, R2 //Compute R1-R2 and update condition codes; //throw away result of subtraction. jmp L //Jump to location L in the code. jmpp L //If P bit is 1, Jump to location L in the code add X, R //Add contents of X,R and store result in R; //Also update the condition codes. Be careful about what type of argument is allowed in the instruction (Memory or Register). Ex. the first argument of ADD instruction is memory, not register. Do Not…Assume a program has 20% store and load. When we run this program in a computer, we observe that L1 instruction cache has a hit rate of 98% and L1 data cache has a hit rate of 96%. The L2 cache has a hit rate of 80%. The access time of L1 cache is 2 cycle, and the access time of L2 cache is 40 cycles. If a miss occurs in L2, we have to go to main memory and the penalty is 100 cycles. Assume that the cache uses physical address.a) Without a TLB, what is the AMAT?b) Assume a TLB is built in the cache and its access time is ignored. If the TLB has a 99% hit rate, what is the new AMAT?c) If there is a 0.01% chance that a page fault happens, and the penalty to fetch a page from the disk is 106cycles, what is the new AMAT?Consider the interfacing of a RAM to an 8086 microprocessor as shown in the figure below. If the starting address of the RAM is 00000H. RAM1 = 64K , RAM2 = 64K , RAM3 = 32K , RAM4 = 64K ,and RAM5 = 32K bytes. What is the address of the last location of RAM3?