(a)

To construct: The table for the state of each transistor.

To find: The output voltage

(a)

Answer to Problem 16.62P

The value of the output voltages is obtained and is shown in Table 2

Explanation of Solution

Calculation:

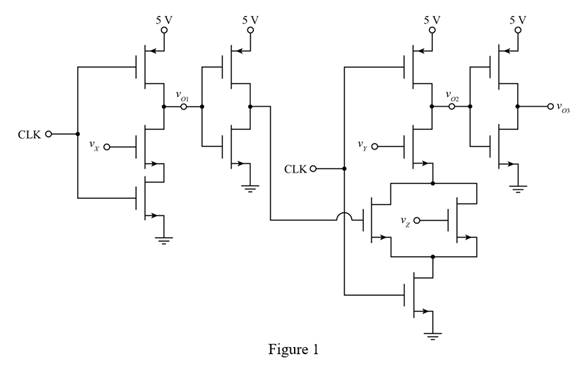

The given diagram is shown in Figure 1

The given table is shown in Table 1

Table 1

| State | CLK | |||

For state 1

The input clock signal input X, Y and Z are at logic zero and the logic function of the output voltage

Substitute

From the circuit the NMOS device with the input

The expression for the logic function of the output voltage

Substitute

The logic function of the output voltage

Substitute

For state 2.

All the inputs are at logic 1.

Substitute

Substitute

Substitute

For state 3.

All the inputs are at logic 0.

Substitute

Substitute

Substitute

For state 4.

The input clock,

Substitute

Substitute

Substitute

For state 5.

All the inputs are at logic zero.

Substitute

Substitute

Substitute

For state 6.

The input clock,

Substitute

Substitute

Substitute

The table for the state of the transistors and the output voltage is shown in table below.

The required table is shown in Table 2

Table 2

| State | CLK | ||||||

The table for the state of the transistor is shown below.

Conclusion:

Therefore, the value of the output voltages is obtained and is shown in Table 2

(b)

The logic function that the circuit implements.

(b)

Answer to Problem 16.62P

The logic that the circuit performs is

Explanation of Solution

Calculation:

The expression for the output voltage

Substitute

Conclusion:

Therefore, the logic that the circuit performs is

Want to see more full solutions like this?

Chapter 16 Solutions

Microelectronics Circuit Analysis and Design

- Q: Show, how to use the ROM circuits to multiply two binary numbers each of two bits.(DSD)arrow_forwardplease explain step by step how to calculate the number of transistors given the logic gates AND, OR, NOT.arrow_forwardDerive expression for output rms voltage of single-phase bridge inverter when using single-pulse-width modulation technique.arrow_forward

- If a 3 phase inverter is feeding an appliance that is rated as 207v AC, 60Hz, 100kVA, compute the minimum DC input voltage, that must be feed to the inverter. Assume the Modulation Index Ma to 1. ...arrow_forwardWhat are the delay and power-delay product for the ECL gate as shown if IEE is changed to 0.5 mA, but the logic swing is maintained the same?arrow_forwardRedraw the circuit using a saturated load transistor. (b) What is the logic functionof the new circuit? (c) What are the W/L ratios ofthe transistors based on the reference inverter design in 6.24(b)?arrow_forward

- Redraw the circuit using a saturated load transistor. (b) What is the logic functionof the new circuit? (c) What are the W/L ratiosof the transistors based upon the reference inverterdesign in. 6.24(b)?arrow_forward19. With necessary diagrams and equations, describe the operation of different types of single-phase PWM inverters. Compare multiple-pulse and sinusoidal pulse modulation schemes with single-phase PWM scheme.arrow_forward(a) A CMOS inverter has (W/L)N =15/1,(W/L)P =15/1, and VDD =3.3V. What is the peakcurrent in the logic gate and at what input voltagedoes it occur? (b) Repeat for VDD =2.5 V.arrow_forward

- What is the advantage of CMOS logic compared to TTL logic?arrow_forwardIf,for a single phase half bridge inverter the amplitude of output voltage is Vs and the output power is P then their corresponding values for a single phase full-bridge inverter are a. 2Vs,2P b. 2Vs,4P c. 2Vs,P d. Vs,Parrow_forwardIntroduce the concept of dynamic logic and domino CMOS logic techniques.arrow_forward

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning

Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education

Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON

Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,

Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,