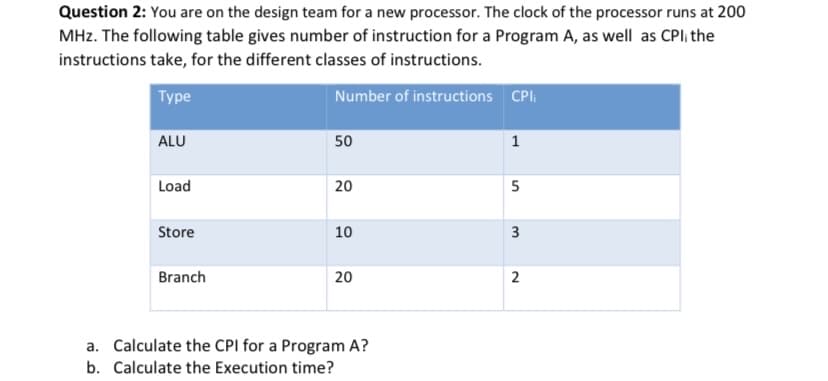

Question 2: You are on the design team for a new processor. The clock of the processor runs at 200 MHz. The following table gives number of instruction for a Program A, as well as CPI, the instructions take, for the different classes of instructions. Турe Number of instructions CPI, ALU 50 Load 20 5 Store 10 Branch 20 a. Calculate the CPI for a Program A? b. Calculate the Execution time? 3. 2)

Q: A processor has the following mix of instruction types, which require different amounts of time to…

A: For executing the instructions total time is evaluated below. Type 1 instruction take 800ps. So…

Q: If you have 5 different instructions and each instruction having 4-stages like (Fetch, Decode,…

A:

Q: Suppose on a non-pipelined single-processor machine, you have the following breakdown: alu…

A: (a)Non-pipelined single-processor machineAverage CPI = (0.25*2 + 0.3*10 + 0.15*4 + 0.3*1.5) = 4.55

Q: Question 2 (8) i) Processor having Clock cycle of 0.25ns will have clock rate of a) 2GHZ b) 3GHZ c)…

A: “Since you have posted a question with multiple sub-parts, we will solve the first three subparts…

Q: Assuming the contents of memory locations 1 and 3 are already in the CPU. Outline the steps involve…

A: Steps involved in adding two number : Read both the operands from the source memory location. Add…

Q: Assume accessing the memory would take 1000 ns and accessing the registers would take 1 ns. Compute…

A: Code Snippet#1: MOV EAX, [0x00089871] Moves the value at memory address 0x00089871 to the EAX…

Q: A program sees a 4% miss rate on both the Instruction Cache and the Data Cache. Every instruction…

A: Answer: Our guidelines is answer the first three question from the first question so we will see…

Q: Outline of Chapter 4 Assignment This is general outline of the assignment. You have to watch all…

A: Note: we only answer up to 3 sub-parts, we’ll answer the first 3. Please resubmit the question and…

Q: Question 1 Using a typical benchmark program, the following machine characteristics result:…

A:

Q: PC Instruction I ADOR Instruction Memory RD RS RT RD RD1 Register File ALU WD RD2 ADDR Data Memory…

A: 1. Pipeline stages There are 5 pipeline stages. They are: Instruction Fetch Instruction decode…

Q: Question 1. Assuming the contents of memory location 1 and 3 are already in the CPU. Outline the…

A: Answer:

Q: Question 2: You are on the design team for a new processor. The clock of the processor runs at 200…

A: Answer to the above question is in sttep2.

Q: Given the following sequence of instructions: lw $s3, 40($s1) //1 lw $s2, 40($s0) //2 add $s1,…

A: Since you are asking multiple questions we are answering first question for you. If you want…

Q: Question: A benchmark program is run on a 80 MHz processor . The executed program consists of 90,000…

A:

Q: 1. Create a gantt chart 2. Compute for the AWT 3. Compute for the ATT 4. Compute for the ART 5.…

A: In FCFS scheduling algorithm, the process which comes first will be served first So, the processes…

Q: Question 1: Single-cycle processor clock A processor has the following mix of instruction types,…

A: Question 2) fastest clock per cycle 800*30% ,200*20% ,250*50% 240 400 125 800ps is the…

Q: Suppose AC is loaded with 0F3C Hex. What is the name of instruction and its job? determine the type…

A: Given, AC is loaded with 0F3C Hex. ie, LOAD AC, @0F3C

Q: The CPU we are talking about today is intel core i7- 8750H write in detail about the below given…

A: specifications : The i7-8750H operates at 2.2 GHz with a TDP of 45 W and a turbo boost of up to 4.1…

Q: We need to model a single cycle full pipelined processor in Verilog Steps: Identify and…

A: Actually, registers are used to stores the data\information.

Q: Question 4 (a) Consider the memory locations shown in Table Q4 (a), explain the architecture of a…

A:

Q: Complete the following table using the codes attributed. Provide how many instructions of the given…

A: Required: Complete the following table using the codes attributed. Provide how many instructions of…

Q: R-type I-type LDUR STUR CBZ B 24% 28% 25% 10% 11% 2% What fraction of all instructions…

A: What fraction of all instructions read from register file? Answer : 24% What fraction of all…

Q: There are 5 Questions. Each Question Carry Assume that there are no pipeline stalls and that the…

A: Given: add:20%, addi:20%, not:0%, beq:25%, Iw:25%, sw:10%. Question 1:In what fraction of all cycles…

Q: How many cycles are required for the pipelined MIPS processor to issue all of the instructions for…

A: 4 + (3 + 4 + 3) X 5 + 3 = 57 clock cycles The number of instructions executed is 1 + (3 X 5) + 1 =…

Q: If R0 = 0x8000 and memory data layout is as below, what are the r1 and r0 register values,…

A: LDR r1, [ro], #4 Here LDR stands for load data from memory into register. [Ro] means the content of…

Q: 8. For a single cycle processor, the instruction breakdown of a program is listed as following. add…

A: The above question is answered in step 2:-

Q: What memory location is accessed by MOV AL, [BX+DI+2080H]? Assume that the DS register contains…

A: Here is the solution:

Q: question 3: please : solution with explain What answer appears in memory locations 1200 hex to 1203…

A: Solution: I am going to solve both the questions one by one with explanation.

Q: Category: CPU Wiring Look at the following (incomplete) diagram of the Hack CPU taken from figure…

A: The central processing unit (CPU) is an electronic machine that executes instructions, which are a…

Q: A computer hardware as the following latency for its instructions in Pico seconds: Type Instruction…

A: AS PER THE BARTLEBY POLICY I HAVE ANSWERD ONLY FIRST QUESTION

Q: The table below shows instruction-type breakdown for different programs. Using this data, you will…

A: The answer is

Q: Question 1: Logic Path and Delay A. Calculate the time to execute the following instructions. B.…

A: for addi addi accesses instruction memory once, register read or write twice , ALU once, adder once…

Q: Question 3 a. As a computer manufacturer you are faced with the challenge of designing quality…

A: Company Guidelines As per our company guidelines we have to answer only the first question . So,…

Q: A program sees a 4% miss rate on both the Instruction Cache and the Data Cache. Every instruction…

A:

Q: 2. Define Pipelining as related to improving processor performance, and then, calculate the number…

A: Given Data : Number of instructions = 5 Number of cycles per stage = 1 To find : Number of…

Q: Q.No.2: For a program execution, Step 1 is completed in the below diagram by filling the required…

A: Actually, PC,IR,AC all these are registers used in computer. PC is a program counter it is used to…

Q: To perform the actions of fetch and execute, all CPU are equipped with the following resources,…

A: This question comes from Digital Electronics which is a paper of Computer Science. Let's discuss it…

Q: Question 2: Problem Solving Suppose that you have a computer with a memory unit of 24 bits per word.…

A: Answer :

Q: Question 8: Consider a 5-stage instruction execution in which, Instruction fetch = ALU operation =…

A: *As per the company norms and guidelines we are providing one question answer only please repost…

Q: 6. Fill in the table below, assuming each instruction can impact the subsequent instructions.…

A: Answer:-(6) a. mov1 -4(%ebp),%eax : // source value 0X6044-4=0x6018 where, DEST will…

Q: The table below shows instruction-type breakdown for different programs. Using this data, you will…

A:

Q: A program sees a 4% miss rate on both the Instruction Cache and the Data Cache. Every instruction…

A: The above question is solved in step 2:-

Q: Suppose we had a processor design with 5 stages where each stage takes the following amount of time:…

A: Suppose we had a processor design with 5 stages where each stage takes the following amount of time:…

Q: Machine A Instruction Count (millions) CPI Arithmetic 8 2 Instruction Class Load/Store 6 4 Branch 7…

A: Cycles per instruction, or CPI, is a metric that has been part of the VTune interface for years. It…

Q: Show the steps of the CPU fetch–execute cycle for the Input and Output instructions. Take ADD…

A: Given Show the steps of the CPU fetch–execute cycle for the Input and Output instructions.

Q: We want to compare the latency and the cycle time of a pipelined and non-pipelined processor design.…

A: A) Pipelining: All the stages take a single clock cycle in pipelining, so the clock cycle must be…

Q: Given the following sequence of instructions: R1 = X + 1 Y = R1 + R2 R1 = R2 + X Complete the…

A: STEP 1:- Given:- R1=X+1 Y=R1+R2 R1=R2+X

Q: Suppose that you have a machine with the following specifications Has AC and Rl registers. The…

A: I'm providing the answer to above both parts. I hope this will meet your requirement

Q: The Figure 1 below shows the Amdahl's law for multiprocessor (speedup vs. number of processors),…

A: - We need to select the correct analysis for the provided graph. - The options :: First option…

Q: Consider computing the overall CPI for a machine Z for which the following performance measures were…

A: The clock rate of the CPU = 200mhz. Instruction Category Percentage of Occurrence No. of cycles…

Trending now

This is a popular solution!

Step by step

Solved in 2 steps with 1 images

- How does pipelining improve CPU efficiency? What’s the potential effect on pipelining’s efficiency when executing a conditional BRANCH instruction? What techniques can be used to make pipelining more efficient when executing conditional BRANCH instructions?8. For a single cycle processor, the instruction breakdown of a program is listed as following. add 20% addi 20% not 0% beq 25% Iw SW 25% 10% What is the percentage of instructions that will use the output of sign extend circuit-module? a. b. What is sign extend circuit-module doing when its output is not needed for current instruction?The CPU design team is designing an instruction set with three classes of instructions. Parameters are given in the following table. Consider a program with 65% ALU instructions, 25% memory access instructions, and 10% control instructions. What is the average CPI for this CPU? Clock Rate 4GHz CPI for ALU Inst. 6 CPI for Memory Inst. 8 CPI for Control Inst. 2

- Explain what you mean by "pipelining" in the context of improving processor speed, and then determine how many cycles it will take to run five instructions assuming each part of the machine requires one cycle. First, we'll look at the situation a) without pipelining and b) with pipelining. There are four ways to do this: a, b, c, and d, all of which include pipelining.Question 5 • What are the actions involved during instruction execution? Explain the Fetch cycle or CPU cycle with a proper diagram. Full explain this question and text typing work only thanksdont give existing answers surely downvote (a) A processor with a clock cycle time of 0.5 nanoseconds has a CPI of 4 for a particular program. What is the MIPS rating for this program? (b) A program is run on a system with two types of machine language instructions: type A instructions each require 3 clock cycles, while type B instructions each require 1 clock cycle. If 100 million type A instructions and 400 million type B instructions are executed, what is the CPI for this program? (c) For a particular program as run on a particular system, the CPU execution time is 1 second, the CPI is 4, and 750 million instructions were executed. What is the clock rate as measured in GHz?

- A benchmark program to evaluate the performance of a processor spends 80% of its time on floating-point commands and 20% on non-floating point commands. A design team wants to obtain an overall speedup of 40% over the existing run time of this benchmark program by speeding up ONLY the non-floating point commands. What should be the ratio of the non-floating point commands new runtime to that of its old runtime? Select the best answer. This is a trick question! In this scenario, it is impossible to speed up only the non-floating point commands to obtain an overall 40% speedup! 2 0.5 2.5You must show all work for every problem that requires it. The point values for problems may be changed at the professor's discretion. Read each question carefully and follow the instructions. A computer hardware as the following latency for its instructions in Pico seconds: Type Instruction Memory Register Read ALU Operation Data Memory Register Write Total R-Format 250 150 200 0 20 620 lw 250 150 200 250 20 870 sw 250 150 200 250 0 850 beq 250 150 200 0 0 600 J 250 0 0 0 0 250 For a single-cycle implementation what Clock Rate does the machine needs to operate at? For a multi-cycle implementation what Clock Rate does the machine needs to operate at? Provide the type, assembly language instruction and binary representation of instructions described by the following MIPS fields: Op=0x0, rs=3, rt=2, rd=3, shamt=0, funct=34 Op=0x23, rs=3, rt=1, const=0x4 In the snippet of assembly code below, how many times is…You are designing a floating point coprocessor which will execute floating point instructions 5 times as fast as the regular processor with zero overhead. Given a workload that contains 25% floating point instructions, what is the speedup achieved by adding the coprocessor to the system? Please give the speedup with exact precision.

- Stella designs a 3 GHz processor where two important programs, A and B, take one second each to execute. Each program has a CPI of 1.5. Sam is tasked with designing the company's next-generation processor and she comes up with an idea that improves the CPI of A to 1.25 and the CPI of B to 1. But the processor can only be implemented with a cycle time of 0.5 ns. Does Sam's new processor out-perform Stella's processor on program A? How about on program B?The ISA of a processor has four classes of instructions: arithmetic, store, load and branch with CPI 2, 4, 4 and 1 respectively. Assume a program composed by 261 arithmetic operations, 829 stores, 262 loads and 130 branches. What is the execution time of the program in a 1.3 GHz processor? Give the result in microseconds (μs).Suppose we had a processor design with 5 stages where each stage takes the following amount of time: IF: 400 ps ID: 200 ps EX: 300 ps MEM: 500 ps WB: 200 psQ1: If you choose a pipelined design, what is the CPI? Assume that we have enough instructions such that the brief ramp up period at the beginning and the ramp down period at the end with less than 100% utilization does not matter. Q2: If you choose a pipelined design, what is the average execution time per instruction in picoseconds?