Computer Systems: A Programmer's Perspective (3rd Edition)

3rd Edition

ISBN: 9780134092669

Author: Bryant, Randal E. Bryant, David R. O'Hallaron, David R., Randal E.; O'Hallaron, Bryant/O'hallaron

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Textbook Question

Chapter 6, Problem 6.31HW

Suppose that a program using the cache in Problem 6.30 references the 1-byte word at address 0x071A. Indicate the cache entry accessed and the cache byte value returned in hex. Indicate whether a cache miss occurs. If there is a cache miss, enter “___” for “Cache byte returned.” Hint Pay attention to those valid bits!

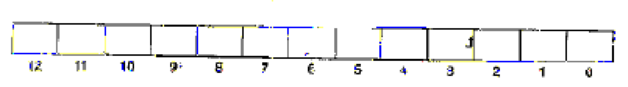

A. Address format (1 bit per box):

B. Memory reference

| Parameter | Value |

| Block offset (CO) | 0x____ |

| Index (CT) | 0x____ |

| Cache tag (CT) | 0x____ |

| Cache hit? (Y/N) | |

| Cache byte returned | 0x____ |

Expert Solution & Answer

Want to see the full answer?

Check out a sample textbook solution

Students have asked these similar questions

A computer of 32 bits has a cache memory of 64 KB with a cache line size of 64 bytes. The cache access time is 20 ns, and the miss penalty is 120 ns. The cache is 2-way associative.

a) What is the number of cache lines?

b) What is the number of cache sets?

c) What is the number of lines per set?

d) Draw a scheme of this cache.

e) Calculate the time to read a word in case of miss.

QUESTION 22

Assume a cache has 16 entries. How many index bits are needed to address the cache?

a.

2

b.

4

c.

5

d.

16

QUESTION 23

Which of the following statements about cache write policy is NOT true?

a.

A dirty bit is used to implement a write back approach.

b.

A cache entry with dirty bit = 1 means the data inside is safe to be replaced.

c.

A write back approach is not suitable for multiple processors accessing the same memory.

d.

A write back approach is typically faster than a write through approach.

QUESTION 25

Which of the following statements is true of normalized scientific notation?

a.

3.06 x 10^3 is in decimal normalized scientific notation

b.

0.30 x 10^3 is in decimal normalized scientific notation

c.

0.11 x 10^5 is in binary normalized scientific notation

d.

10.01 x 10^5 is in binary normalized scientific notation

Suppose a computer using direct mapped cache has 232 byte of byte-addressable main memory, and a cache of 1024 blocks, where each cache block contains 32 bytes.

a) How many blocks of main memory are there?

b) What is the format of a memory address as seen by the cache, i.e., what are the sizes of the tag, block, and offset fields?

c) To which cache block will the memory address 0x000063FA map?

Chapter 6 Solutions

Computer Systems: A Programmer's Perspective (3rd Edition)

Ch. 6.1 - Prob. 6.1PPCh. 6.1 - Prob. 6.2PPCh. 6.1 - Prob. 6.3PPCh. 6.1 - Prob. 6.4PPCh. 6.1 - Prob. 6.5PPCh. 6.1 - Prob. 6.6PPCh. 6.2 - Prob. 6.7PPCh. 6.2 - Prob. 6.8PPCh. 6.4 - Prob. 6.9PPCh. 6.4 - Prob. 6.10PP

Ch. 6.4 - Prob. 6.11PPCh. 6.4 - Prob. 6.12PPCh. 6.4 - Prob. 6.13PPCh. 6.4 - Prob. 6.14PPCh. 6.4 - Prob. 6.15PPCh. 6.4 - Prob. 6.16PPCh. 6.5 - Prob. 6.17PPCh. 6.5 - Prob. 6.18PPCh. 6.5 - Prob. 6.19PPCh. 6.5 - Prob. 6.20PPCh. 6.6 - Prob. 6.21PPCh. 6 - Prob. 6.22HWCh. 6 - Prob. 6.23HWCh. 6 - Suppose that a 2 MB file consisting of 512-byte...Ch. 6 - The following table gives the parameters for a...Ch. 6 - The following table gives the parameters for a...Ch. 6 - Prob. 6.27HWCh. 6 - This problem concerns the cache in Practice...Ch. 6 - Suppose we have a system with the following...Ch. 6 - Suppose we have a system with following...Ch. 6 - Suppose that a program using the cache in Problem...Ch. 6 - Repeat Problem 6.31 for memory address0x16E8 A....Ch. 6 - Prob. 6.33HWCh. 6 - Prob. 6.34HWCh. 6 - Prob. 6.35HWCh. 6 - Prob. 6.36HWCh. 6 - Prob. 6.37HWCh. 6 - Prob. 6.38HWCh. 6 - Prob. 6.39HWCh. 6 - Given the assumptions in Problem 6.38, determine...Ch. 6 - You are writing a new 3D game that you hope will...Ch. 6 - Prob. 6.42HWCh. 6 - Prob. 6.43HWCh. 6 - Prob. 6.45HWCh. 6 - Prob. 6.46HW

Additional Engineering Textbook Solutions

Find more solutions based on key concepts

Describe a situation where memberwise assignment is not desirable.

Starting Out with C++ from Control Structures to Objects (8th Edition)

Write an SQL statement to display the pet ID, breed, and type for all pets having a four-character name startin...

Database Concepts (8th Edition)

Celsius to Fahrenheit Table In one of the Chapter 3 Programming Challenges you were asked to write a program th...

Starting Out with C++: Early Objects (9th Edition)

In Exercises 33 through 40, determine the output displayed in the list box by the lines of code.

Introduction to Programming Using Visual Basic (10th Edition)

Array Operations Write a program with an array that is initialized with test data. Use any primitive data type ...

Starting Out with Java: From Control Structures through Objects (6th Edition)

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Similar questions

- Suppose a computer using direct mapped cache has 2^32 bytes of byte-addressable main memory, and a cache size of 512 bytes, and each cache block contains 64 bytes. a) how many blocks of main memory are there? b) what is the format of a memory address as seen by cache, i.e., what are the sizes of the tag, block, and offset fields? c) to which cache block will the memory address 13A4498A map?arrow_forwardCA_6 We study the properties of cache memory, and for reasons of easier design and efficient circuits, we assume that the cache capacity is 2i Bytes, and cache line size is 2j Bytes, with i and j being natural numbers: (a) How many bits should the tag field have? And can the tag field contain 0 bit (i.e., be empty)? Elaborate (b) Repeat the above for the index field. (c) Repeat the above for the byte-offset field. (d) Finally, depict a figure showing a cache line, indicate what fields it possibly has, state the possible sizes of these fields, and explain the uses of these fields.arrow_forwardComputer Science Consider a direct-mapped cache with 8 lines, each holding 16 bytes of data. The cache is byte-addressable and the main memory consists of 64 KB, which is also byte-addressable. Assume that a program reads 16KB of memory sequentially. Answer the following questions:a) How many bits are required for the tag, index, and offset fields of a cache address?b) What is the cache size in bytes?c) What is the block size in bytes?d) What is the total number of blocks in main memory?e) How many cache hits and misses will occur for the program, assuming that the cache is initially empty?f) What is the hit ratio?g) Give an example virtual address (in BINARY) that will be placed in cache line 5.arrow_forward

- A computer using a direct mapped cache has 220 Bytes of memory (byte addressable) and a cache of 32 blocks, each block contains 16 Bytes. a. How many blocks of main memory are there? b. What will be the sizes of the tag, index, and byte offset fields? c. To which cache set will the memory address 0x0DB63 map?arrow_forwardAssume we have a computer with 512 blocks of cache memory with a total capacity of 128K bits. Answer the following questions knowing that the computer operates in a word addressable mode and that the format of the memory address as perceived by the Fully associative cache scheme is as shown below: Cache Format with Full Associativity 19 5 1- How many words are in each cache block? 2- How big are the letters in each word? 3- How large is the primary memory? 4- What is the total number of blocks in main memory? 5- Draw the memory address format as observed by the Direct Mapped Cache technique, including the fields and their sizes.arrow_forwardSuppose that immediately following the two read operations of question 1,the program does read operations on the following memory addresses (e.g., with “lb”or “lw” instructions): 148, 224, 556, 248 (again), 6728, 1312 (again), and 128.Assuming the cache was empty prior to the read operations of question 1, state whichof these read operations will result in cache hits, assuming a 2-way set-associativecache with a total capacity of 4 eight-word blocks and LRU replacement in each set. Suppose that a program does read operations on the following memory addresses (e.g., with “lb” or “lw” instructions): 248, 1312. Give the number of the memory block that each of these addresses belongs to, for each of the following memory block sizes. A. block size of one word (4 bytes) B. block size of eight words (32 bytes) just do the first partarrow_forward

- Assume you have a cache/memory system with the following characteristics: Size of a word: 4 bytes Size of a cache block: 4 words Size of cache: 16 words Associativity of the cache: 2-way Set Associative. Replacement Policy: LRU (Least Recently Used) How many sets are present in this cache? Assume that the following word addresses are accessed as read in the following order. In each case, say whether or not the corresponding access is a hit or a miss. If it is a miss, specify what kind of miss it is. Words accessed: 4, 3, 6, 8, 1, 24, 16, 19, 20, 19, 1. What is the miss rate for this cache and this pattern of word accesses? Draw a figure showing the final state of the cache.arrow_forwardSuppose a computer using fully associative cache has 224 bytes of byte-addressable main memory and a cache of 128 blocks, where each cache block contains 64 bytes. a) How many blocks of main memory are there? b) What is the format of a memory address as seen by the cache, i.e., what are the sizes of the tag and offset fields? c) To which cache block will the memory address 0x01D872 map?arrow_forwarda) Assume that a direct mapped cache memory stores 1024 blocks and 64 bytes per block.i) What is storage capacity of the cache memory in bytes?ii) What is length of tag bits if 20 bits addressing is used in CPU?b) Draw a table indicating the initial state (Valid, Tag bits and Data) of a direct mapped cache with 8-blocks and 1 word per block. (Assume that words have 5-bits address length). Then, fill / modify the table (valid, tag and data columns) by accessing word-addresses below in given order. (e.g. old value → new value → ...)5, 10, 26, 5, 10, 23, 20, 5, 23, 10(Show memory accesses by writing Mem[Word Address] in “Data” column)c) Which accesses are “hit” and which accesses are “miss” in question (b)?5, 10, 26, 5, 10, 23, 20, 5, 23, 10arrow_forward

- Suppose we have a system with the following properties:The memory is byte addressable.Memory accesses are to 1-byte words (not to 4-byte words).Addresses are 13 bits wide.The cache is 4-way set associative (E = 4), with a 4-byte block size(B = 4) and eight sets (S = 8).Consider the following cache state. All addresses, tags, and valuesare given in hexadecimal format. The Index column contains the set index for each set of four lines. The Tag columns contain the tag value for each line. The V columns contain the valid bit for each line. The Bytes 0−3 columns contain the data for each line, numbered left to right starting with byte 0 on the left. A. What is the size (C) of this cache in bytes?B. The box that follows shows the format of an address (1 bit perbox). Indicate (by labeling the diagram) the fields that would beused to determine the following:CO. The cache block offsetCI. The cache set indexCT. The cache tagarrow_forwardSuppose a computer using direct mapped cache has 4G Bytes of main memory and a cache of 256 Blocks, where each cache Block has 16 Words, and Word Size is 4 Bytes. a)How many blocks of main memory? b)What is the format of a memory address as seen by the cache (Tag, Block and Word fields)? c)To which cache block will the memory reference 0000146A in Hex?arrow_forwardConsider the following main memory word reference string; start with an empty cache all blocks initially marked as not valid Using Spatial Locality: 1 3 5 1 0 7 2 4 1 3 Find the number of requests? Find the number of Hits? Find the number of Misses?arrow_forward

arrow_back_ios

arrow_forward_ios

Recommended textbooks for you

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON

Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON

Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON

C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning

Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Database System Concepts

Computer Science

ISBN:9780078022159

Author:Abraham Silberschatz Professor, Henry F. Korth, S. Sudarshan

Publisher:McGraw-Hill Education

Starting Out with Python (4th Edition)

Computer Science

ISBN:9780134444321

Author:Tony Gaddis

Publisher:PEARSON

Digital Fundamentals (11th Edition)

Computer Science

ISBN:9780132737968

Author:Thomas L. Floyd

Publisher:PEARSON

C How to Program (8th Edition)

Computer Science

ISBN:9780133976892

Author:Paul J. Deitel, Harvey Deitel

Publisher:PEARSON

Database Systems: Design, Implementation, & Manag...

Computer Science

ISBN:9781337627900

Author:Carlos Coronel, Steven Morris

Publisher:Cengage Learning

Programmable Logic Controllers

Computer Science

ISBN:9780073373843

Author:Frank D. Petruzella

Publisher:McGraw-Hill Education

Instruction Format (With reference to address); Author: ChiragBhalodia;https://www.youtube.com/watch?v=lNdy8HREvgo;License: Standard YouTube License, CC-BY