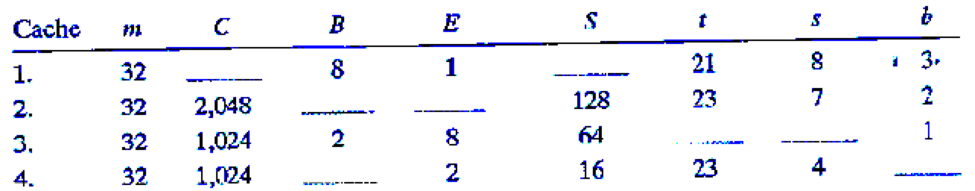

The following table gives the parameters for a number of different caches. Your task is to fill in the missing fields in the table. Recall that m is the number of physical address bits, C is the cache size (number of data bytes), B is the block size in bytes, E is the associativity, S is the number of cache sets, t is the number of tag bits, s is the number of set index bits, and b is the number of block offset bits.

Want to see the full answer?

Check out a sample textbook solution

Chapter 6 Solutions

Computer Systems: A Programmer's Perspective (3rd Edition)

Additional Engineering Textbook Solutions

Starting Out with Java: From Control Structures through Objects (7th Edition) (What's New in Computer Science)

Starting Out with Java: Early Objects (6th Edition)

Starting Out With Visual Basic (8th Edition)

Experiencing MIS

Starting Out with C++ from Control Structures to Objects (9th Edition)

C Programming Language

- For a direct-mapped cache design with a 32-bit address, the following bitsof the address are used to access the cache. Use the table below. a. What is the cache block size (in words)?b. How many entries does the cache have?c. What is the ration between total bits required for such a cache implementation overthe data storage bit?arrow_forwardBelow is a list of 32-bit memory address references, given as memory addresses. 12, 720, 172, 8, 764, 352, 760, 56, 724, 176, 744You would like to access a cache with the given memory addresses. The size of cache is 23 = 8-blocks. Your task is to: (1) find out the binary address, (2) fill out the tag and index for each memory address and (3) indicate whether the access is hit or miss in the following table:arrow_forwardSuppose a computer using direct-mapped cache has 232 (that's 232)232) bytes of byte-addressable main memory, and a cache size of 512 bytes, and each cache block contains 64 bytes. How many blocks of main memory are there? What is the format of a memory address as seen by cache, i.e. what are the sizes of the tag, block, and offset fields? To which cache block will the memory address 0x13A4498A map?arrow_forward

- For a direct-mapped cache design with a 32-bit address, the following bits of the address areused to access the cache.Tag Index Offset31–10 9–6 5–0a– What is the cache block size (in words)? b – How many entries does the cache have? c – What is the ratio between total bits required for such a cache implementation overthe data storage bits?arrow_forwardHere is the question: A direct-mapped cache consists of 8 blocks. A byte-addressable main memory contains 4K blocks of eight bytes each. Access time for the cache is 20 ns and the time required to fill a cache slot from main memory is 300 ns. Assume a request is always started in sequential to cache and then to main memory. If a block is missing from cache, the entire block is brought into the cache and the access is restarted. Initially, the cache is empty. b) Compute the hit ratio for a program that loops 3 times from address 0 to 75 (base 10) in memory. For b, another example has been provided in regards to a previous problem: A direct-mapped cache consists of eight blocks. Main memory contains 4K blocks of eight words each. Access time for the cache is 22 ns and the time required to fill a cache slot from main memory is 300ns (this time will allow us to determine the block is missing and bring it into cache). Assume a request is always started in parallel to both cache and to…arrow_forwardQUESTION 22 Assume a cache has 16 entries. How many index bits are needed to address the cache? a. 2 b. 4 c. 5 d. 16 QUESTION 23 Which of the following statements about cache write policy is NOT true? a. A dirty bit is used to implement a write back approach. b. A cache entry with dirty bit = 1 means the data inside is safe to be replaced. c. A write back approach is not suitable for multiple processors accessing the same memory. d. A write back approach is typically faster than a write through approach. QUESTION 25 Which of the following statements is true of normalized scientific notation? a. 3.06 x 10^3 is in decimal normalized scientific notation b. 0.30 x 10^3 is in decimal normalized scientific notation c. 0.11 x 10^5 is in binary normalized scientific notation d. 10.01 x 10^5 is in binary normalized scientific notationarrow_forward

- 1. For a direct-mapped cache design with a 32-bit address, the following bits of address are used to access the cache. Tag Index Offset 31-14 13-7 6-0 a. What is the cache block size (in words)? b. How many entries does this cache have? c. What is the ratio between total bits required for such a cache implementation over the data storage bits?arrow_forwardThe following code, written in C, where elements within the same row are stored contiguously, was implemented on a computer system containing the cache system already discussed.for( i = 0; i < 8; i++ )for( j = 0; j<8000; j++ )a[i][j] = b[i][0] + a[j][i]a) References to which variables exhibit temporal locality?b) References to which variables exhibit spatial locality? (please explain in details)arrow_forwardDetermine the cache performance of the following code:1 for (i = 0; i < 16; i++){2 for (j = 0; j < 16; j++) {3 total_x += grid[j][i].x;4 total_y += grid[j][i].y;5 }6 }A. What is the total number of reads?B. What is the total number of reads that miss in thecache?C. What is the miss rate?D. What would the miss rate be if the cache were twice asbig?arrow_forward

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON

Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON

Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON

C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning

Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education