Computer Systems: A Programmer's Perspective Plus Mastering Engineering With Pearson Etext -- Access Card Package (3rd Edition)

3rd Edition

ISBN: 9780134123837

Author: Randal E. Bryant, David R. O'Hallaron

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Textbook Question

Chapter 6, Problem 6.40HW

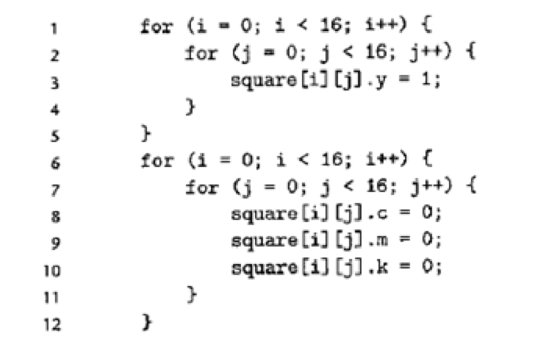

Given the assumptions in Problem 6.38, determine the cache performance of the following code:

- A. What is the total number of writes?

- B. What is the total number of writes that miss in the cache?

- C. C What is the miss rate?

Expert Solution & Answer

Want to see the full answer?

Check out a sample textbook solution

Students have asked these similar questions

The following table gives the parameters for a number of differentcaches. Your task is to fill in the missing fields in the table. Recall that m is the number of physical address bits, C is the cache size (number of data bytes), B is the block size in bytes, E is the associativity, S is the number of cache sets, t is the number of tag bits, s is the number of set index bits, and b is the number of block offset bits.

This function will be able to determine the fields in a log entry it needs to look at in

order to do its job properly. The following line of code computes the average number

of cache misses for each item in the cache when 64-byte cache blocks are used

without any prefetching being performed by the program.

Problem 0. The following table gives some of the parameters for a number of different hardware

caches. Fill in the table with the values of the missing parameters. Recall that m is the number of

physical address bits, C is the cache size in bytes, B is the block size in bytes, E is the associativity,

i.e., lines per set, S is the number of sets, t is the number of tag bits, s is the number of set index

bits, and b is the number of block offset bits.

Cache m

48

32030

(b)

48

32

24

24

C

B

E

16384 32 16

32768 64

65536 128

512 32

1024

8

8

4

14

1

4

S

b

S

t

Chapter 6 Solutions

Computer Systems: A Programmer's Perspective Plus Mastering Engineering With Pearson Etext -- Access Card Package (3rd Edition)

Ch. 6.1 - Prob. 6.1PPCh. 6.1 - Prob. 6.2PPCh. 6.1 - Prob. 6.3PPCh. 6.1 - Prob. 6.4PPCh. 6.1 - Prob. 6.5PPCh. 6.1 - Prob. 6.6PPCh. 6.2 - Prob. 6.7PPCh. 6.2 - Prob. 6.8PPCh. 6.4 - Prob. 6.9PPCh. 6.4 - Prob. 6.10PP

Ch. 6.4 - Prob. 6.11PPCh. 6.4 - Prob. 6.12PPCh. 6.4 - Prob. 6.13PPCh. 6.4 - Prob. 6.14PPCh. 6.4 - Prob. 6.15PPCh. 6.4 - Prob. 6.16PPCh. 6.5 - Prob. 6.17PPCh. 6.5 - Prob. 6.18PPCh. 6.5 - Prob. 6.19PPCh. 6.5 - Prob. 6.20PPCh. 6.6 - Prob. 6.21PPCh. 6 - Prob. 6.22HWCh. 6 - Prob. 6.23HWCh. 6 - Suppose that a 2 MB file consisting of 512-byte...Ch. 6 - The following table gives the parameters for a...Ch. 6 - The following table gives the parameters for a...Ch. 6 - Prob. 6.27HWCh. 6 - This problem concerns the cache in Practice...Ch. 6 - Suppose we have a system with the following...Ch. 6 - Suppose we have a system with following...Ch. 6 - Suppose that a program using the cache in Problem...Ch. 6 - Repeat Problem 6.31 for memory address0x16E8 A....Ch. 6 - Prob. 6.33HWCh. 6 - Prob. 6.34HWCh. 6 - Prob. 6.35HWCh. 6 - Prob. 6.36HWCh. 6 - Prob. 6.37HWCh. 6 - Prob. 6.38HWCh. 6 - Prob. 6.39HWCh. 6 - Given the assumptions in Problem 6.38, determine...Ch. 6 - You are writing a new 3D game that you hope will...Ch. 6 - Prob. 6.42HWCh. 6 - Prob. 6.43HWCh. 6 - Prob. 6.45HWCh. 6 - Prob. 6.46HW

Additional Engineering Textbook Solutions

Find more solutions based on key concepts

Suppose you have a chess program that can evaluate 10 million nodes per second. Decide on a compact representat...

Artificial Intelligence: A Modern Approach

What is a variable that is used to accumulate a total called?

Starting out with Visual C# (4th Edition)

3.12 (Date Create a class called Date that includes three pieces Of information as data

members—a month (type ...

C++ How to Program (10th Edition)

Can you reference an instance variable by name within the definition of a non-static method without using a cla...

Java: An Introduction to Problem Solving and Programming (7th Edition)

A pet store sells dogs, cats, birds, and hamsters. Write a declaration for an enumerated data type that can rep...

Starting Out with Java: Early Objects (6th Edition)

Write a function void switchEnds(int array, int size); that is passed the address of the beginning of an array ...

Starting Out with C++: Early Objects

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Similar questions

- The following table gives the parameters for a number of differentcaches. For each cache, fill in the missing fields in the table. Recallthat m is the number of physical address bits, C is the cache size(number of data bytes), B is the block size in bytes, E is theassociativity, S is the number of cache sets, t is the number of tag bits, S is the number of set index bits, and b is the number of block offset bits.arrow_forwardThe following blocks are referenced by the CPU and to be fetched from the RAM to the cache sequentially: (ij k L L jmj n L mj m L k sįPi o k) Assume that the cache set is empty and all the above blocks can be inserted into the set. Use the LRU algorithm to fill in the following table that describes the status of the cache locations for each called block .arrow_forwardFor the following loop, assume the array arr2[][] has never been referenced before in the code. Also assume that a cache line is 32 Bytes, and an int is 4 Bytes. 1. How many memory references are there?2. How many cache misses are there?arrow_forward

- The memory access time is I nanosecond for read operation with a hit in cache. * nanoseconds for a read operation with a miss in cache, 2 nanoseconds for a write operation with a hit in cache and 10 anoseconds for a write operation with a miss in cache. Execution of a sequence of instructions involves 100 instruction fetch operations, 60 memory operand read operations and 40 memory operand write operations. The cache hit-ratio is 0.9. The average memory access time (in nanoseconds) in executing the sequence of instructions isarrow_forwardLet's pretend that something unexpected happens: the CPU makes a partially-completed request to the cache at the same time as a block is being returned from the write buffer to main memory. The following steps need to take place.arrow_forwardBelow is a list of 32-bit memory address references, given as memory addresses. 12, 720, 172, 8, 764, 352, 760, 56, 724, 176, 744You would like to access a cache with the given memory addresses. The size of cache is 23 = 8-blocks. Your task is to: (1) find out the binary address, (2) fill out the tag and index for each memory address and (3) indicate whether the access is hit or miss in the following table:arrow_forward

- The following blocks are referenced by the CPU and to be fetched from the RAM to the cache sequentially: (i j k L L j m j n L m j m L k S j P i O k) Assume that the cache set is empty and all the above blocks can be inserted into the set. Use the LRU algorithm to fill in the following table that describes the status of the cache locations for each called block. Note : All numbers must be binaryarrow_forwardA 2-way set associative cache consists of four sets. Main memory contains 2K blocks of eight words each. Show the main memory address format that allows us to map addresses from main memory to cache. Be sure to include the fields as well as their sizes. Compute the hit ratio for a program that loops 6 times from locations 8 to 51 in main memory. You may leave the hit ratio in terms of a fraction. Please show details how you obtain the result.arrow_forwardWhich of the following statements are generally true? (A) Memory hierarchies take advantage of temporal locality. (B) On a read, the value returned depends on which blocks are in the cache. (C) Most of the cost of the memory hierarchy is at the highest level. (D) Most of the capacity of the memory hierarchy is at the lowest level. (E) Set-Associative cache technique is in the middle between direct-mapped and fully- associative ones.arrow_forward

- 17. A file system uses an in-memory cache to cache disk blocks. The miss rate of the cache is shown in the figure. The latency to read a block from the cache is 1 ms and to read a block from the disk is 10 ms. Assume that the cost of checking whether a block exists in thearrow_forwardExercise 2: A byte addressable memory has a size of 1024 MBytes. This memory is attached to a direct mapping cache of 32KBytes that contains 1024 lines. a. What is the memory address length? b. What is the block size? c. What is the number of blocks in main memory? d. What is the length in bit of: tag (T), line number (L) and byte number (W)? e. Determine in Hexadecimal the tag (T), line number (L) and byte number (W) of the following Hexadecimal memory address: 000008AE f. What is the block that contains the address 000000DE? g. Which line of the cache can hold the block containing 000000DE?arrow_forwardJob list: Job Number Memory Requested J1 700k J2 500k J3 740k Memory List Memory Block Size Block 1 610k (low - order memory) 850k Block 2 Block 3 700k (high - order memory) a.) Use the best-fit algorithm to allocate the memory blocks to the three arriving jobs b.) Use the first-fit algorithm to allocate the memory blocksto the three arriving jobsarrow_forward

arrow_back_ios

SEE MORE QUESTIONS

arrow_forward_ios

Recommended textbooks for you

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON

Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON

Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON

C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning

Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Database System Concepts

Computer Science

ISBN:9780078022159

Author:Abraham Silberschatz Professor, Henry F. Korth, S. Sudarshan

Publisher:McGraw-Hill Education

Starting Out with Python (4th Edition)

Computer Science

ISBN:9780134444321

Author:Tony Gaddis

Publisher:PEARSON

Digital Fundamentals (11th Edition)

Computer Science

ISBN:9780132737968

Author:Thomas L. Floyd

Publisher:PEARSON

C How to Program (8th Edition)

Computer Science

ISBN:9780133976892

Author:Paul J. Deitel, Harvey Deitel

Publisher:PEARSON

Database Systems: Design, Implementation, & Manag...

Computer Science

ISBN:9781337627900

Author:Carlos Coronel, Steven Morris

Publisher:Cengage Learning

Programmable Logic Controllers

Computer Science

ISBN:9780073373843

Author:Frank D. Petruzella

Publisher:McGraw-Hill Education

Instruction Format (With reference to address); Author: ChiragBhalodia;https://www.youtube.com/watch?v=lNdy8HREvgo;License: Standard YouTube License, CC-BY