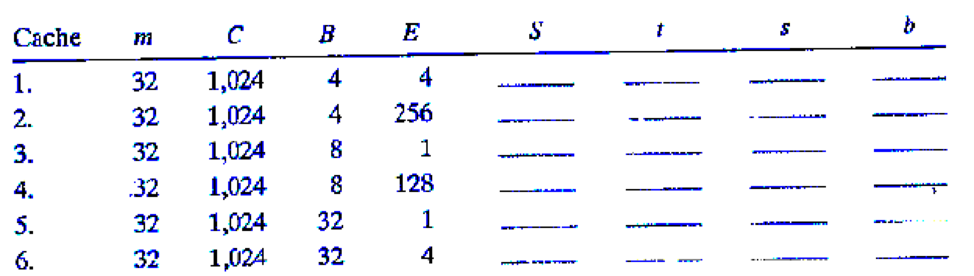

The following table gives the parameters for a number of different caches. For each cache, fill in the missing fields in the table. Recall that m is the number of physical address bits, C is the cache size (number of data bytes), B is the block size in bytes, E is the associativity, S is the number of cache sets, t is the number of tag bits, s is the number of set index bits, and b is the number of block offset bits.

Want to see the full answer?

Check out a sample textbook solution

Chapter 6 Solutions

Computer Systems: A Programmer's Perspective Plus Mastering Engineering With Pearson Etext -- Access Card Package (3rd Edition)

Additional Engineering Textbook Solutions

Java How to Program, Early Objects (11th Edition) (Deitel: How to Program)

Database Concepts (8th Edition)

Modern Database Management

C Programming Language

Concepts Of Programming Languages

Computer Science: An Overview (13th Edition) (What's New in Computer Science)

- A computer of 32 bits has a cache memory of 64 KB with a cache line size of 64 bytes. The cache access time is 20 ns, and the miss penalty is 120 ns. The cache is 2-way associative. a) What is the number of cache lines? b) What is the number of cache sets? c) What is the number of lines per set? d) Draw a scheme of this cache. e) Calculate the time to read a word in case of miss.arrow_forwardSuppose a computer using direct-mapped cache has 232 (that's 232)232) bytes of byte-addressable main memory, and a cache size of 512 bytes, and each cache block contains 64 bytes. How many blocks of main memory are there? What is the format of a memory address as seen by cache, i.e. what are the sizes of the tag, block, and offset fields? To which cache block will the memory address 0x13A4498A map?arrow_forwardProblem 0. The following table gives some of the parameters for a number of different hardware caches. Fill in the table with the values of the missing parameters. Recall that m is the number of physical address bits, C is the cache size in bytes, B is the block size in bytes, E is the associativity, i.e., lines per set, S is the number of sets, t is the number of tag bits, s is the number of set index bits, and b is the number of block offset bits. Cache m 48 32030 (b) 48 32 24 24 C B E 16384 32 16 32768 64 65536 128 512 32 1024 8 8 4 14 1 4 S b S tarrow_forward

- The following table gives the parameters for a number of different caches. For each cache, determine the number of cache sets (S), tag bits (t), set index bits (s), and block offset bits (b). Drag the appropriate labels to their respective targets. Note: not all labels will be used. Reset Help 1 0 2 3 4 5 6 7 8 9 10 15 11 12 13 20 21 22 24 27 28 29 30 31 32 38 48 128 218 256 Cache BE 1. 4 1 2. 8 4 3. 32 32 m C 32 1,024 32 1,024 32 1,024 S 1000 t 음 b 1000 1000 14 220arrow_forwardA cache is set up with a block size of 32 words. There are 64 blocks in cache and set up to be 4-way set associative. You have byte address 0x8923. Show the word address, block address, tag, and index Show each access being filled in with a note of hit or miss. You are given word address and the access are: 0xff, 0x08, 0x22, 0x00, 0x39, 0xF3, 0x07, 0xc0.arrow_forwardProblem 2. The following table gives the parameters for a number of different caches. For each cache, fill in the missing fields in the table. Recall that m is the number of physical address bits, C is the cache size (number of data bytes), B is the block size in bytes, E is the associativity, S is the number of cache sets, t is the number of tag bits, s is the number of set index bits, and b is the number of block offset bits. Cache m C BES tsb 1 32 2048 256 2183 2372 2 32 4 4 3 32 1,024 8 64 256 4 |32|1,024|32|2| 16 5arrow_forward

- Suppose a computer using fully associative cache has 220220 words of main memory and a cache of 128 blocks, where each cache block contains 16 words. (a) How many blocks of main memory are there? (b) What is the format of a memory address as seen by the cache, that is, what are the sizes of the tag and word fields? (c) To which cache block will the memory reference 01D872_{16}01D872_{16} map?arrow_forwardQ: A digital computer has a memory unit of 64k * 16 and a cache memory of 1k words. The cache uses direct mapping with a block size of 4 words. i) How many bits are there in the tag, index, block & words fields of the address formats. ii) How many bits are there in each word of cache? iii) How many blocks can the cache accommodate?arrow_forwardFor a direct-mapped cache design with a 32-bit address, the following bits of the address are used to access the cache: Tag Index Offset 31-10 9-6 5-0 1. What is the cache block size (in words)? 2. How many entries does the cache have? 3. What is the ratio between total bits required for such a cache implementation over the data storage bits?arrow_forward

- Suppose a byte-addressable computer using set-associative cache has 216 bytes of main memory and a cache of 32 blocks, and each cache block contains 8 bytes.Q.) If this cache is 2-way set associative, what is the format of a memory address as seen by the cache; that is, what are the sizes of the tag, set, and offset fields?arrow_forwardFor a direct-mapped cache design with a 32-bit address, the following bits of the address are used to access the cache.Tag Index Offset31–10 9–5 4–01. What is the cache block size (in words)?2. How many entries does the cache have?3. What is the ratio between total bits required for such a cache implementation over the data storage bits?Starting from power on, the following byte-addressed cache references are recorded. Address 0 4 16 132 232 160 1024 30 140 3100 180 2180 How many blocks are replaced? What is the hit ratio? List the fi nal state of the cache, with each valid entry represented as a record of <index, tag, data>arrow_forwardComputer Science Consider a direct-mapped cache with 8 lines, each holding 16 bytes of data. The cache is byte-addressable and the main memory consists of 64 KB, which is also byte-addressable. Assume that a program reads 16KB of memory sequentially. Answer the following questions:a) How many bits are required for the tag, index, and offset fields of a cache address?b) What is the cache size in bytes?c) What is the block size in bytes?d) What is the total number of blocks in main memory?e) How many cache hits and misses will occur for the program, assuming that the cache is initially empty?f) What is the hit ratio?g) Give an example virtual address (in BINARY) that will be placed in cache line 5.arrow_forward

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON

Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON

Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON

C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning

Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education